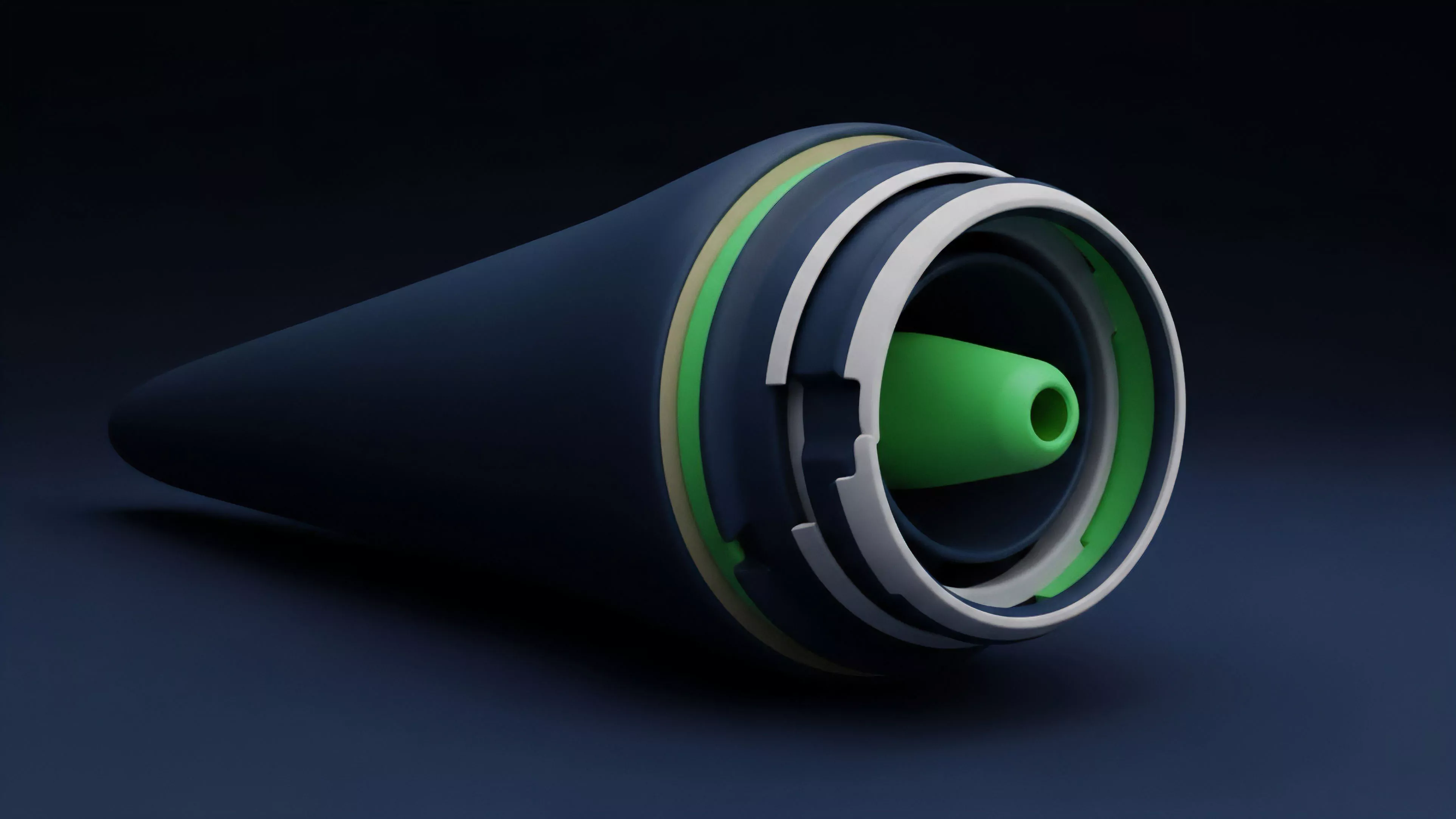

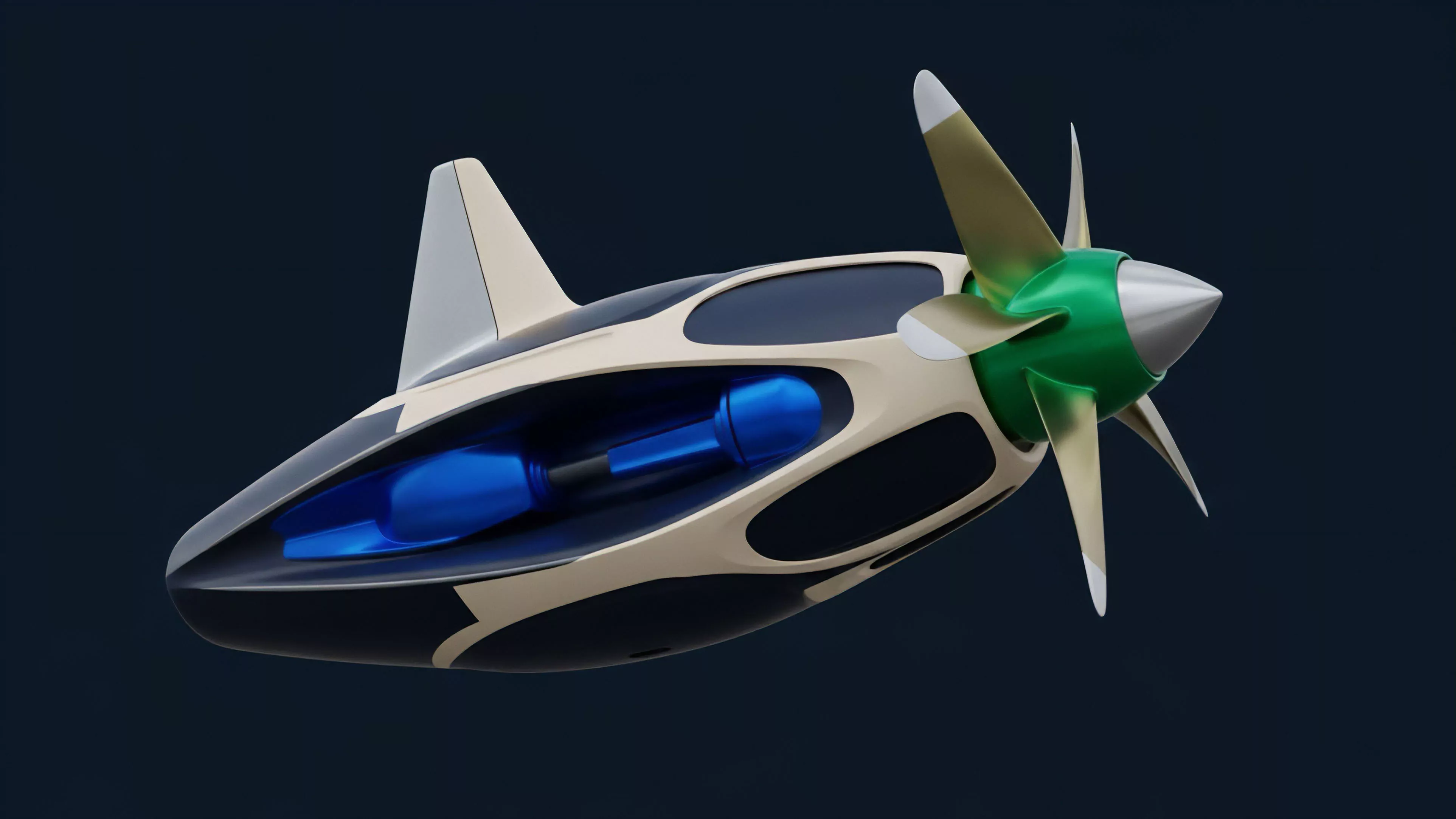

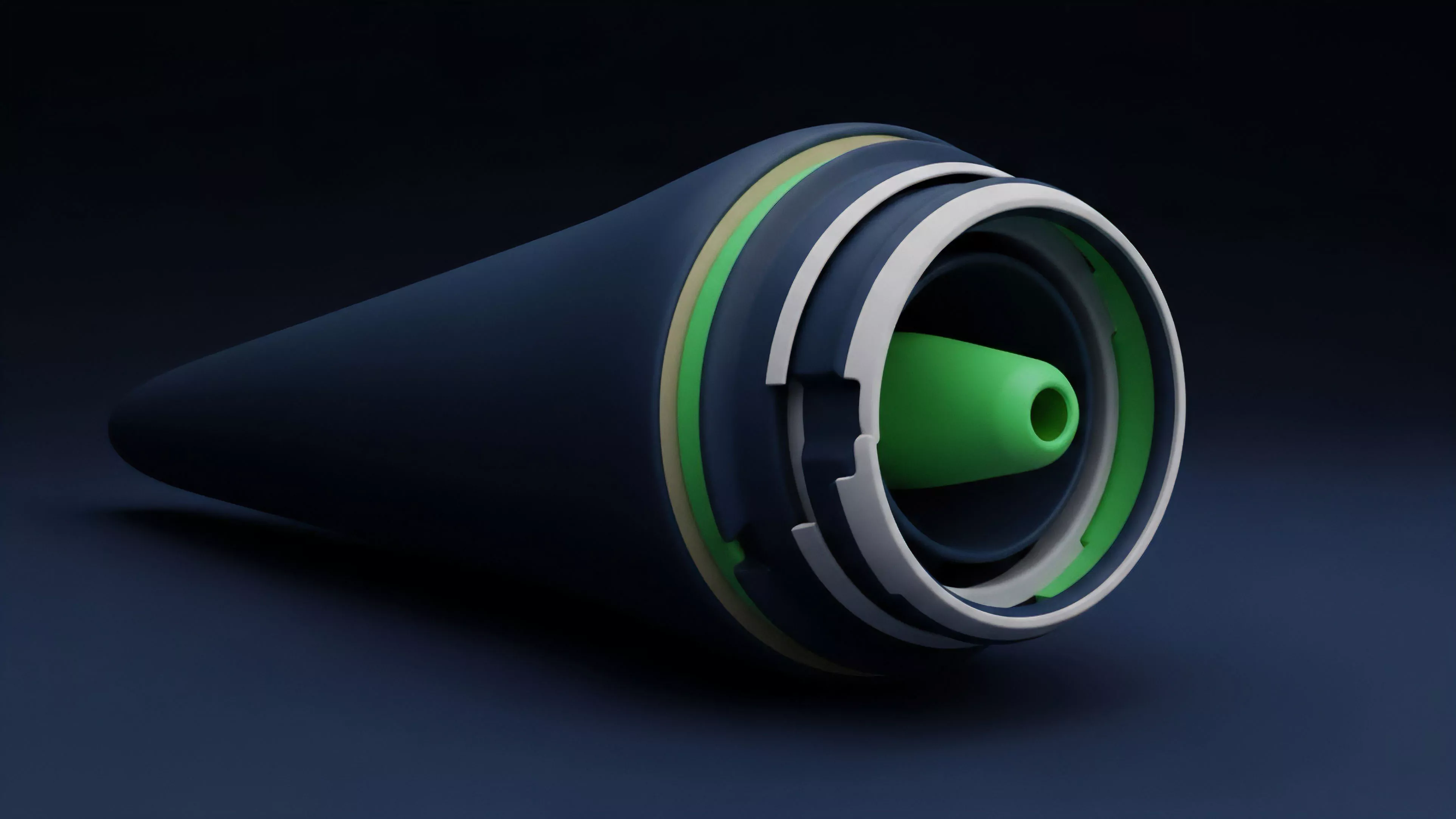

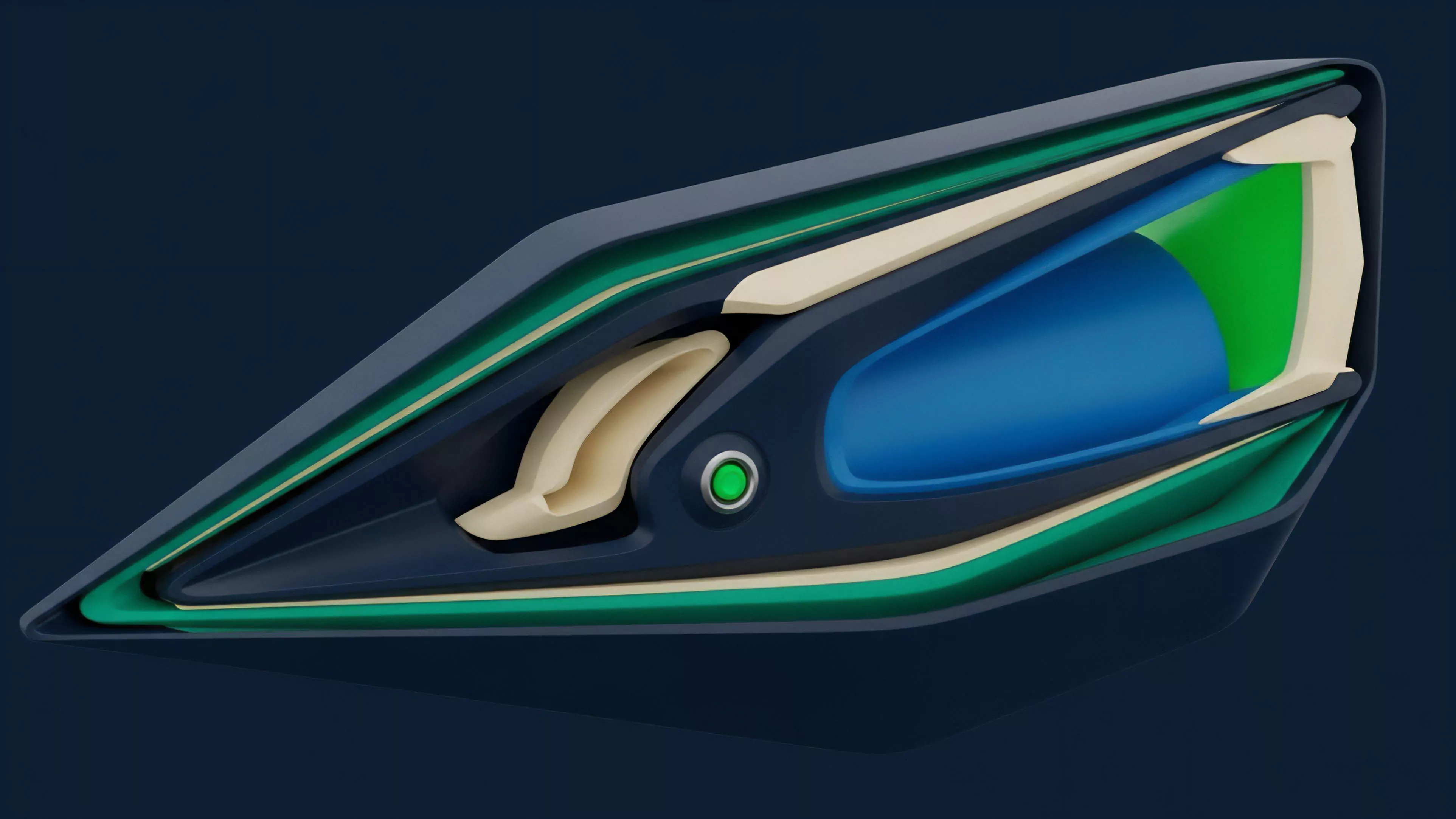

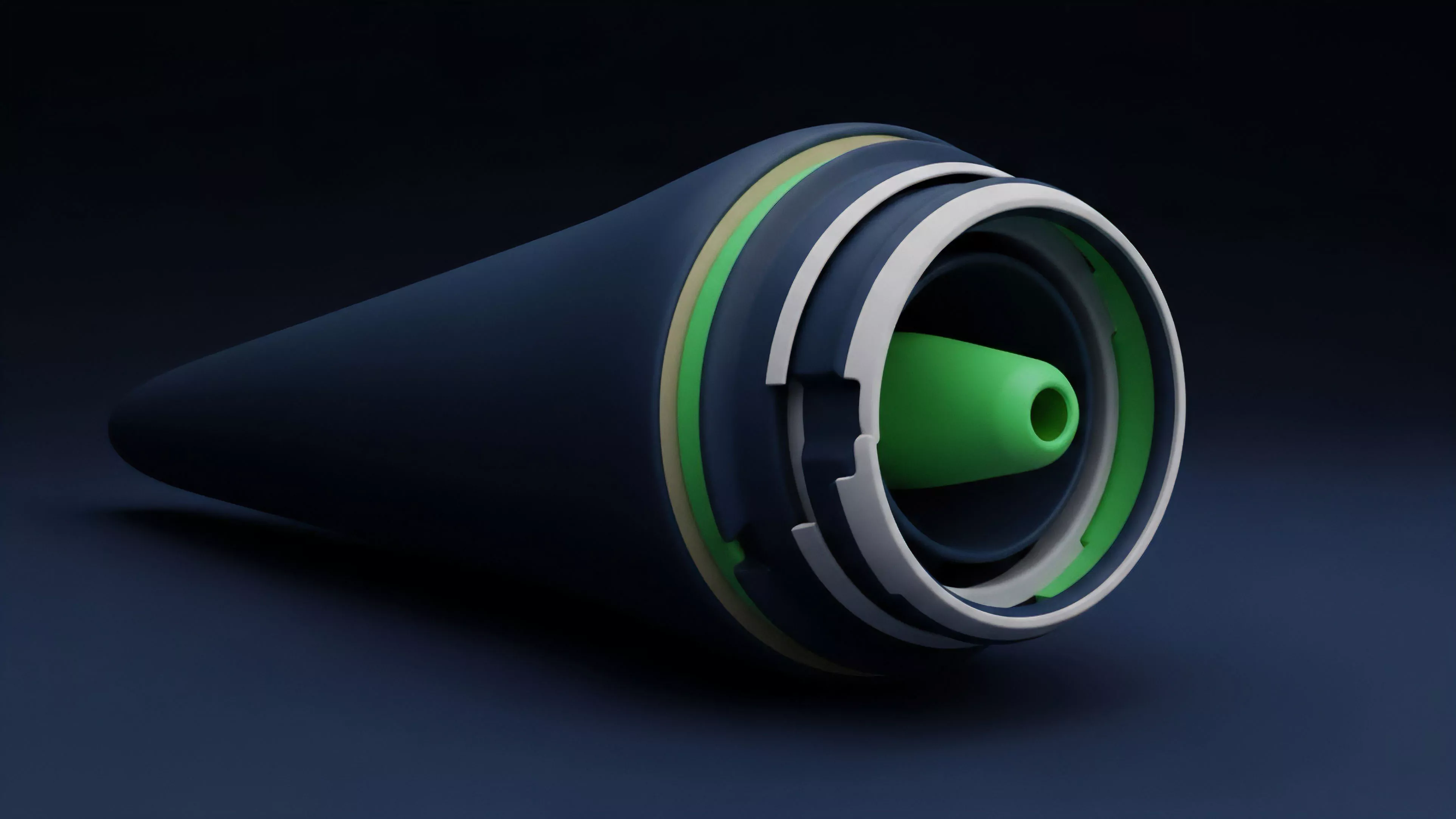

Zero Knowledge Prover

Meaning ⎊ Zero Knowledge Prover facilitates private, verifiable derivative settlement by enabling computational integrity without exposing sensitive data.

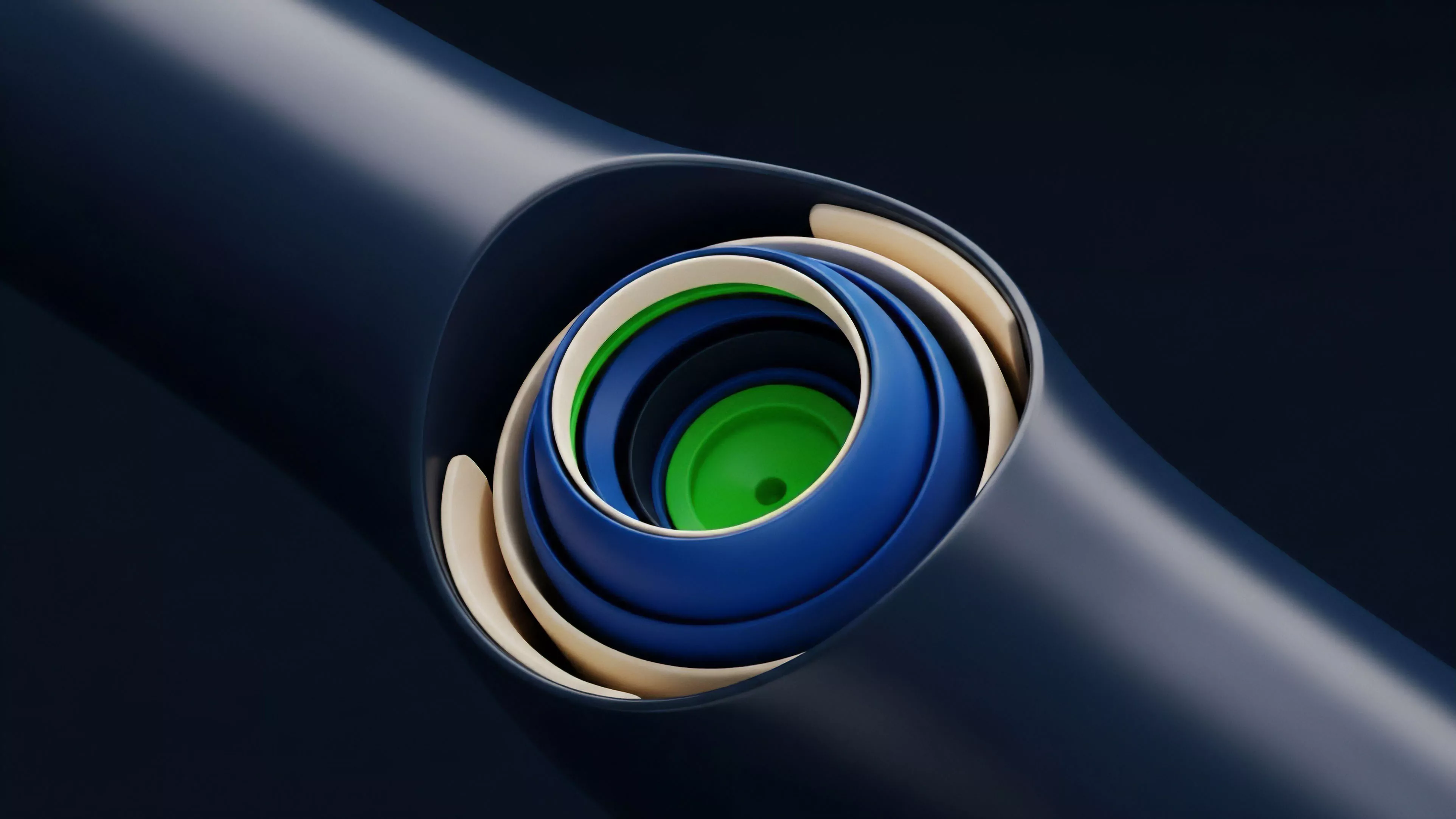

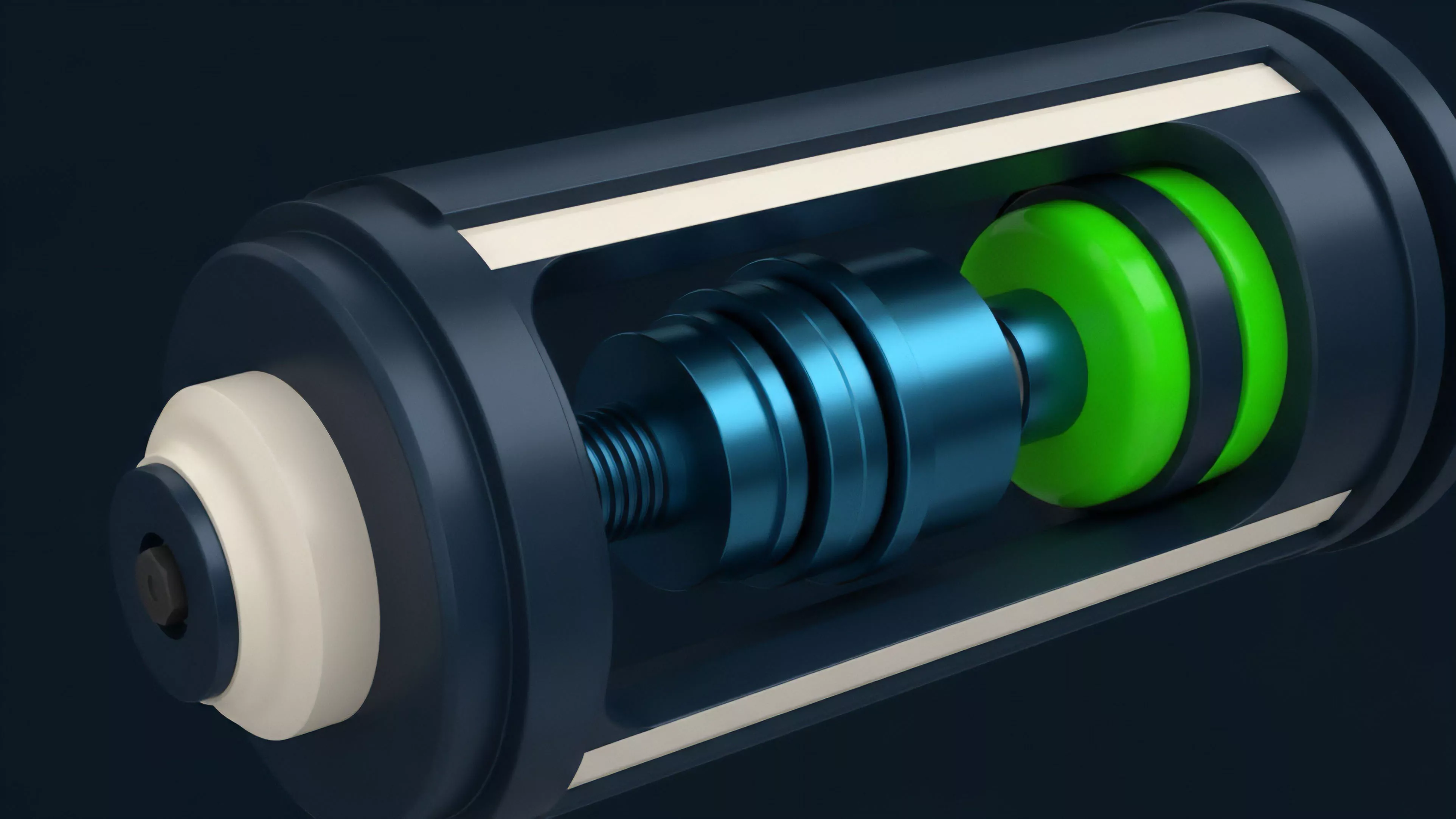

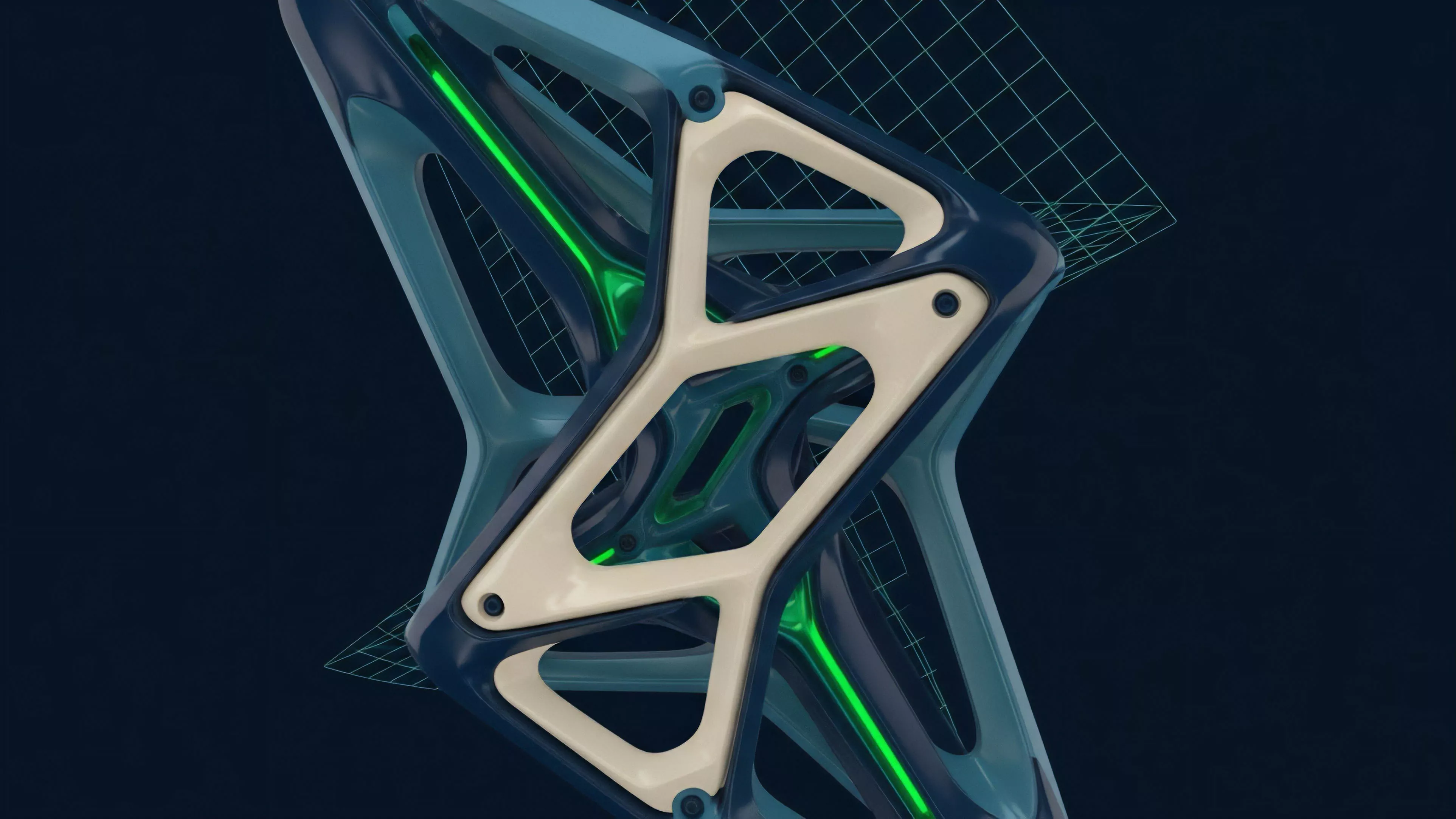

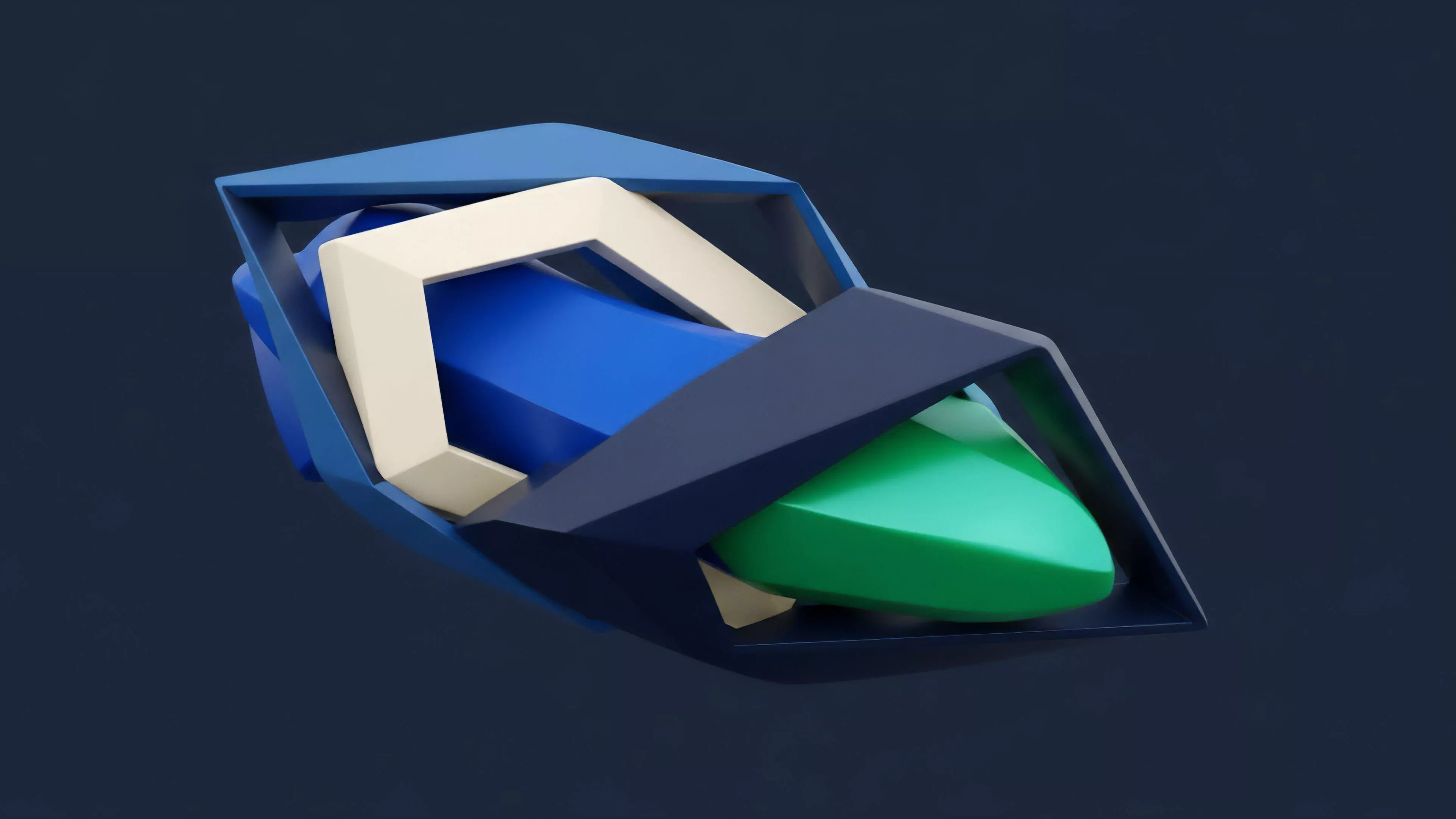

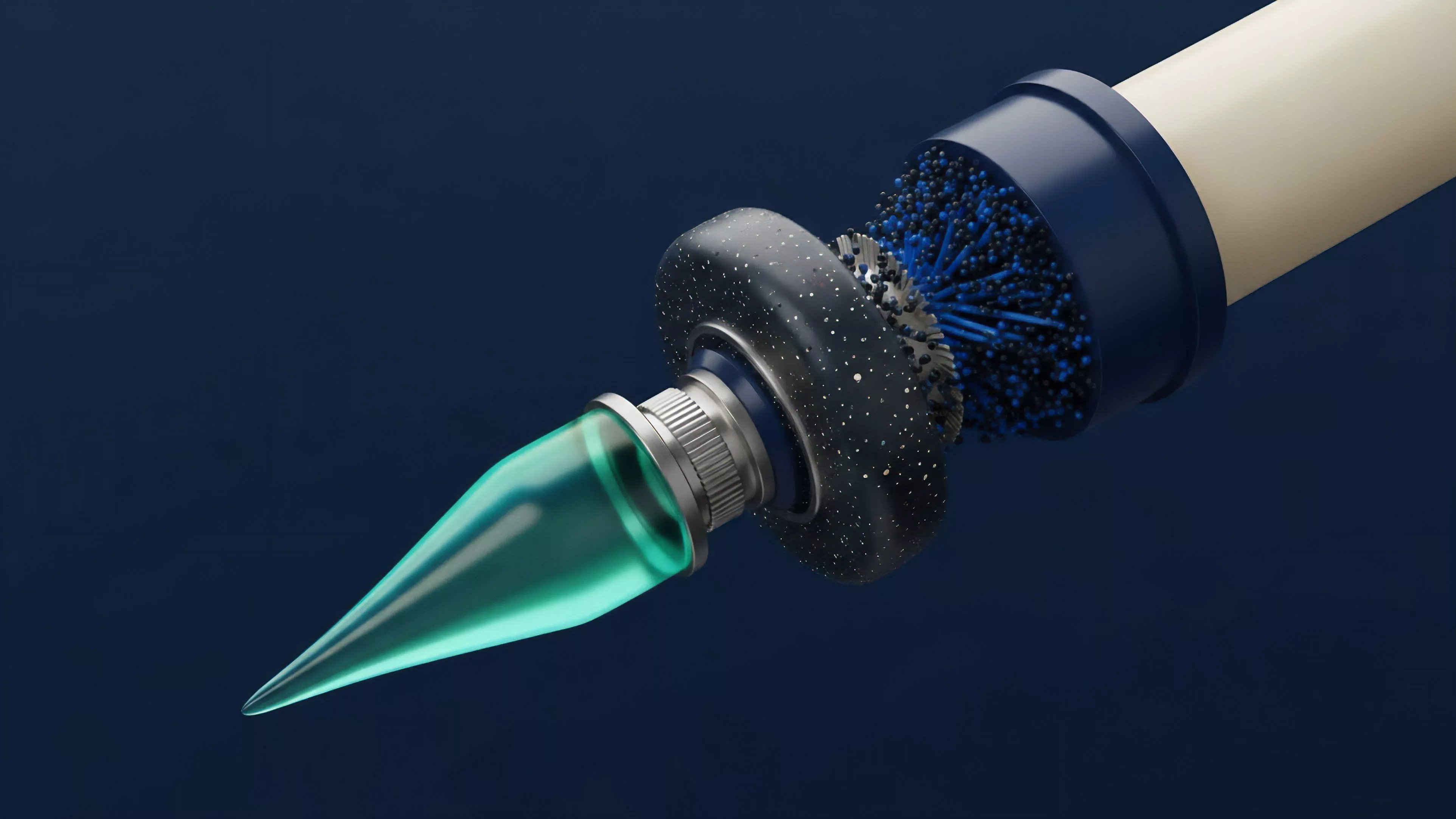

Multi Prover Model

Meaning ⎊ Multi Prover Model establishes cryptographic redundancy by requiring consensus across independent proof systems to eliminate single points of failure.

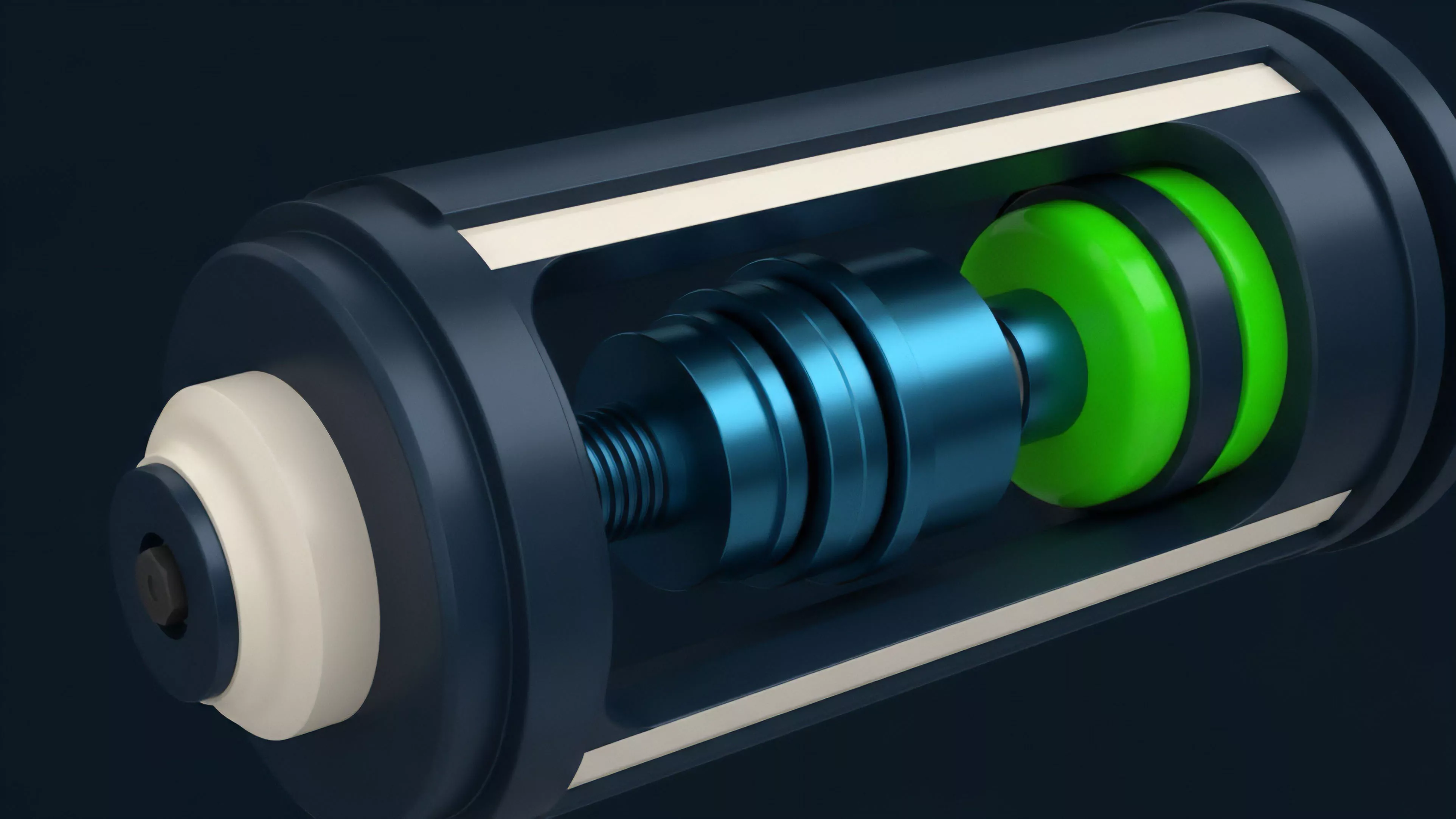

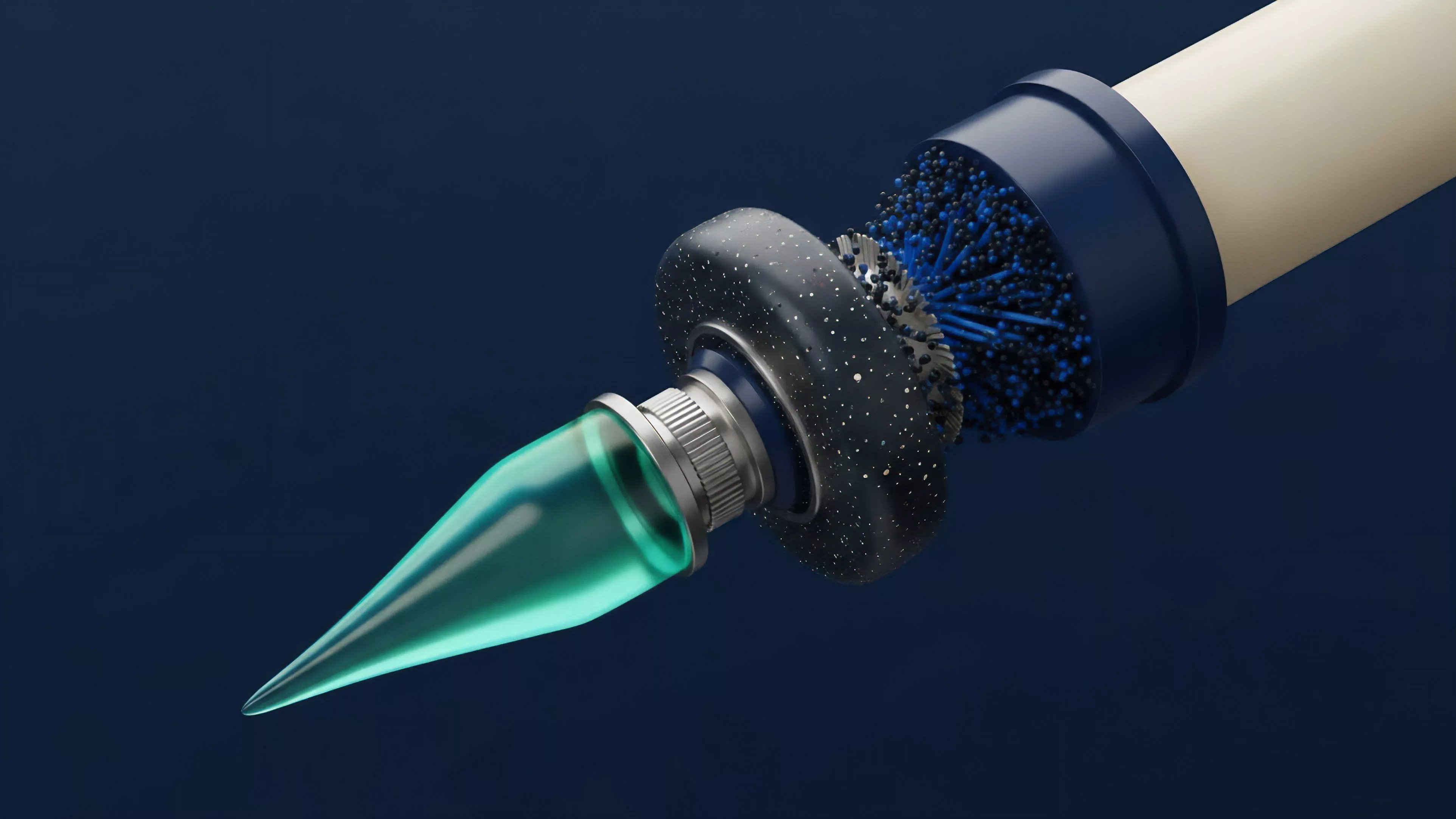

Cryptographic Proof Optimization Strategies

Meaning ⎊ Cryptographic Proof Optimization Strategies reduce computational overhead and latency to enable scalable, privacy-preserving decentralized finance.

Cryptographic Proof Complexity Tradeoffs and Optimization

Meaning ⎊ Cryptographic Proof Complexity Tradeoffs and Optimization balance prover resources and verifier speed to secure high-throughput decentralized finance.

Cryptographic Proof Complexity Optimization and Efficiency

Meaning ⎊ Cryptographic Proof Complexity Optimization and Efficiency enables the compression of vast financial computations into succinct, trustless certificates.

Cryptographic Proof Optimization Techniques and Algorithms

Meaning ⎊ Cryptographic Proof Optimization Techniques and Algorithms enable trustless, private, and high-speed settlement of complex derivatives by compressing computation into verifiable mathematical proofs.

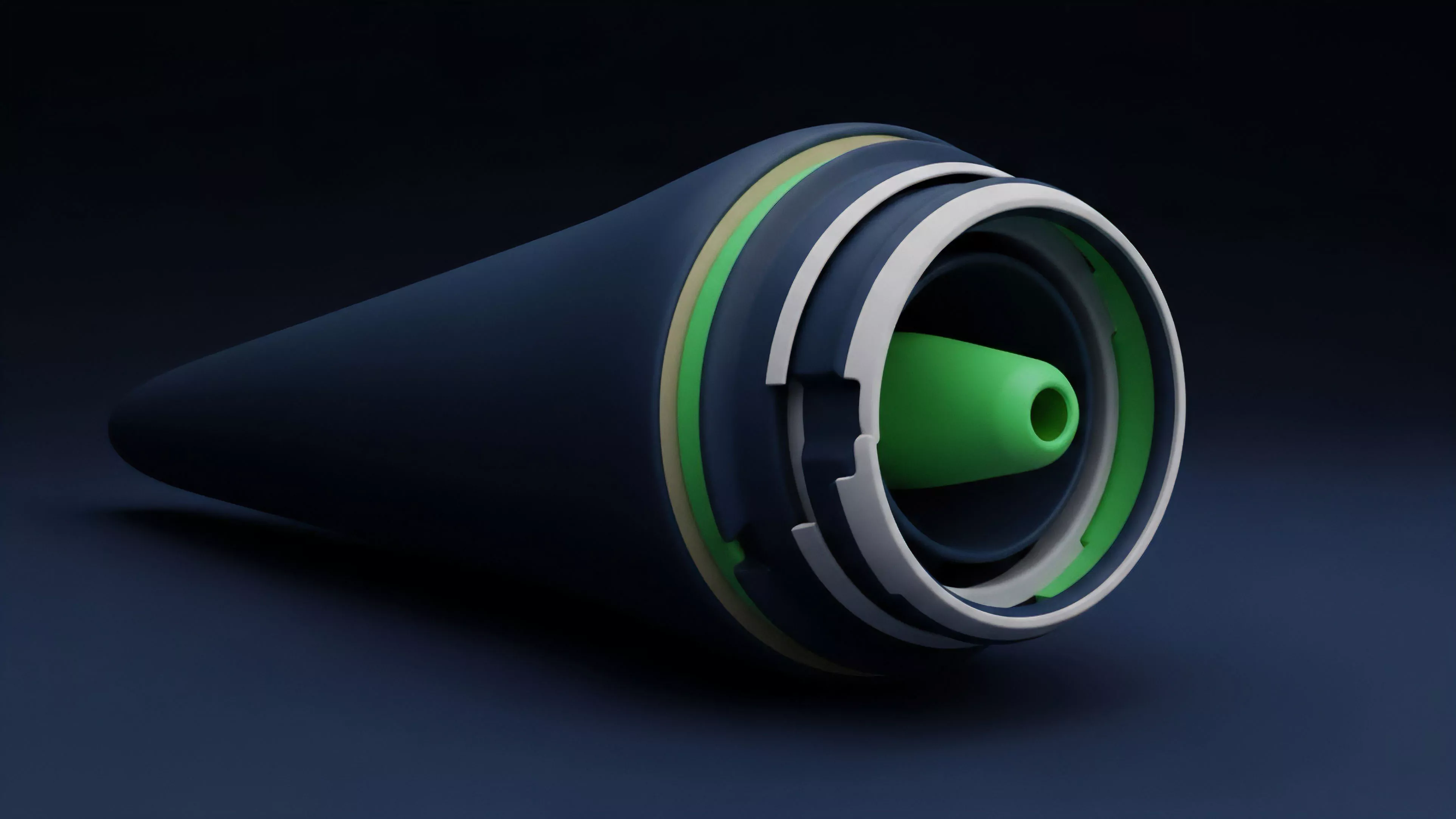

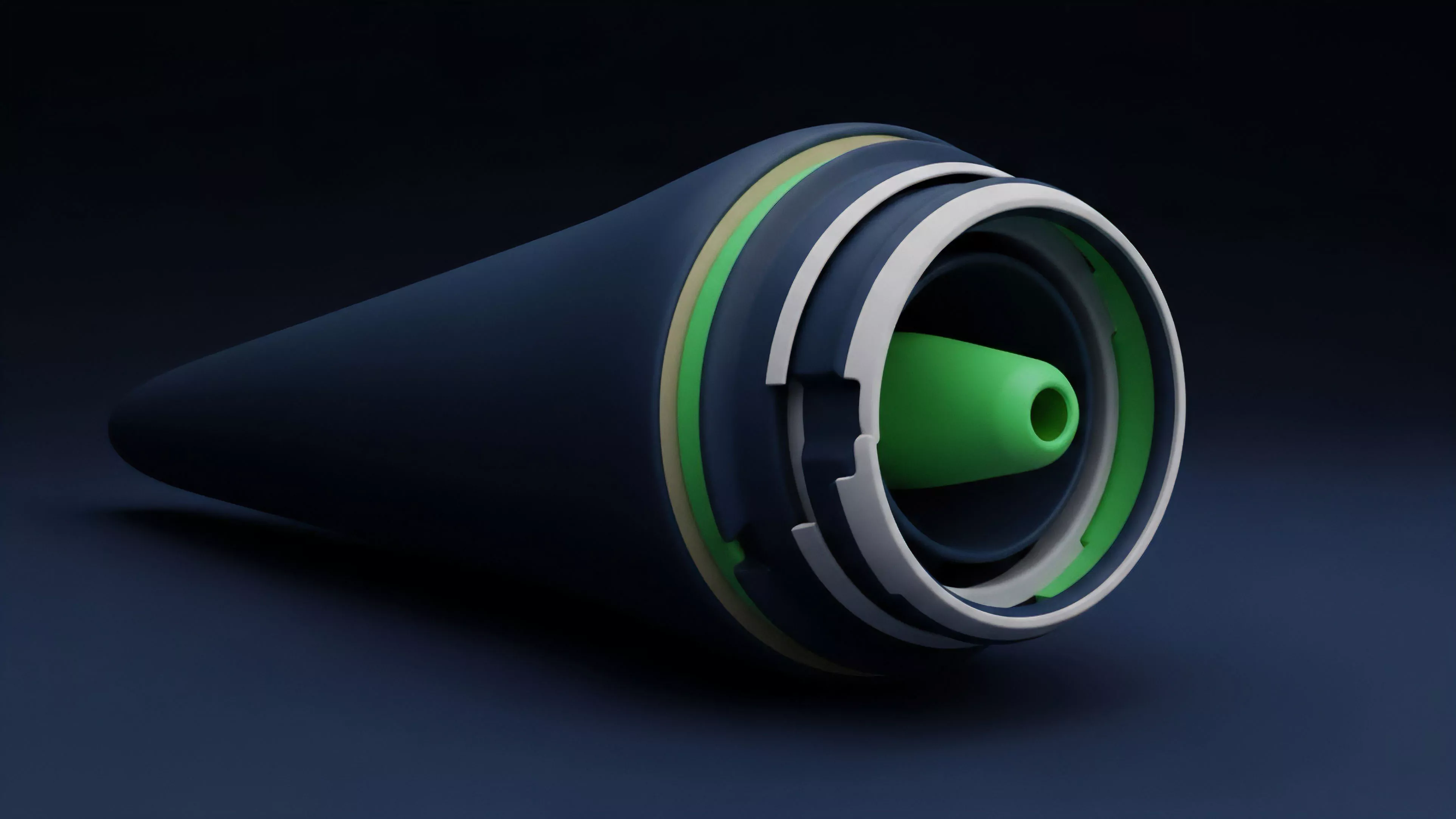

Prover Efficiency

Meaning ⎊ Prover Efficiency determines the operational ceiling for high-frequency decentralized derivatives by linking computational latency to settlement finality.

Liquidation Threshold Optimization

Meaning ⎊ Liquidation Threshold Optimization calibrates the mathematical boundary between capital efficiency and systemic insolvency within decentralized markets.

Order Book Optimization Algorithms

Meaning ⎊ Order Book Optimization Algorithms manage the mathematical mediation of liquidity to minimize execution costs and systemic risk in digital markets.

Order Book Order Flow Optimization

Meaning ⎊ DOFS is the computational method of inferring directional conviction and systemic risk by synthesizing fragmented, time-decaying order flow across decentralized options protocols.

Order Book Order Flow Optimization Techniques

Meaning ⎊ Adaptive Latency-Weighted Order Flow is a quantitative technique that minimizes options execution cost by dynamically adjusting order slice size based on real-time market microstructure and protocol-level latency.

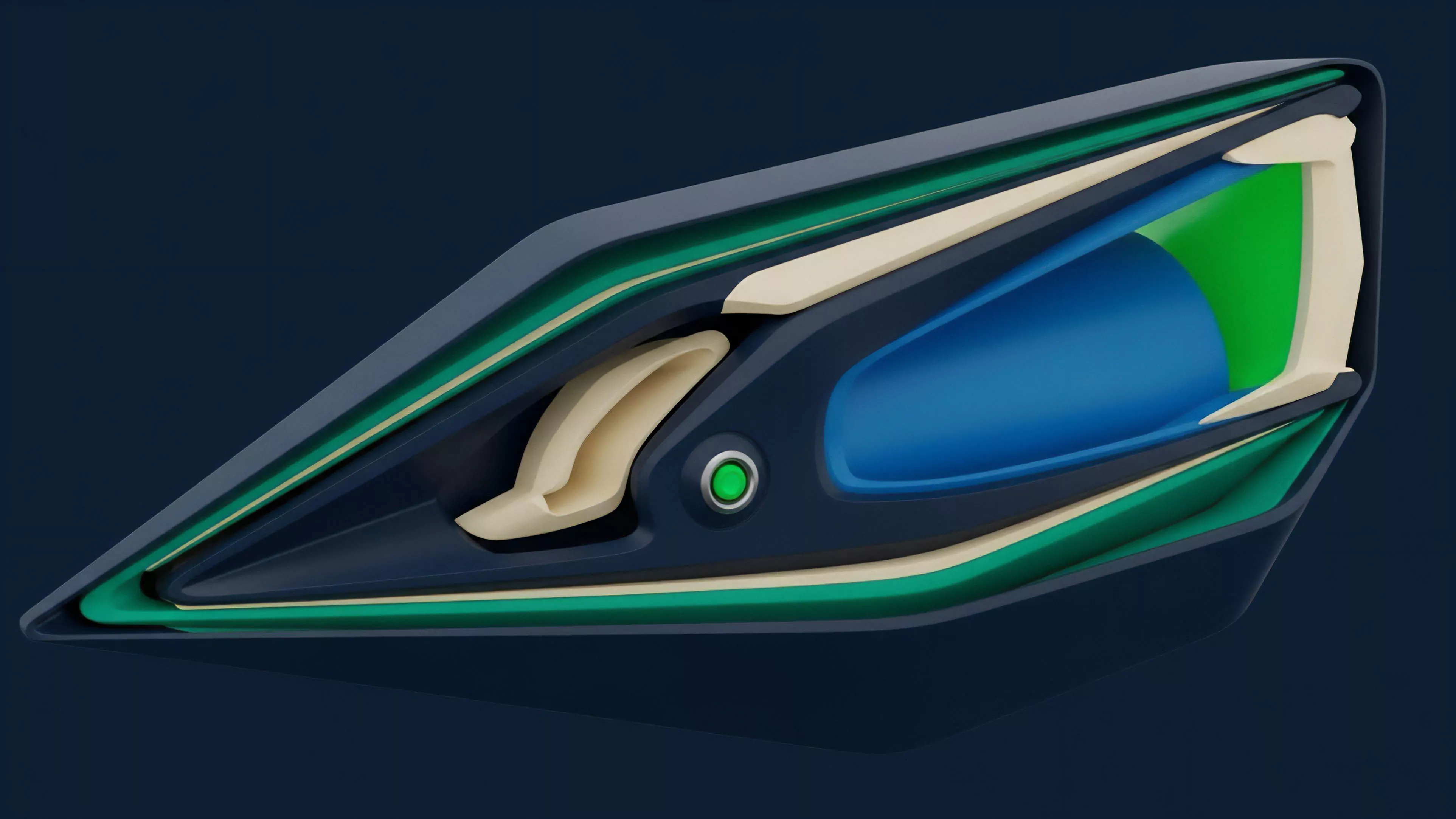

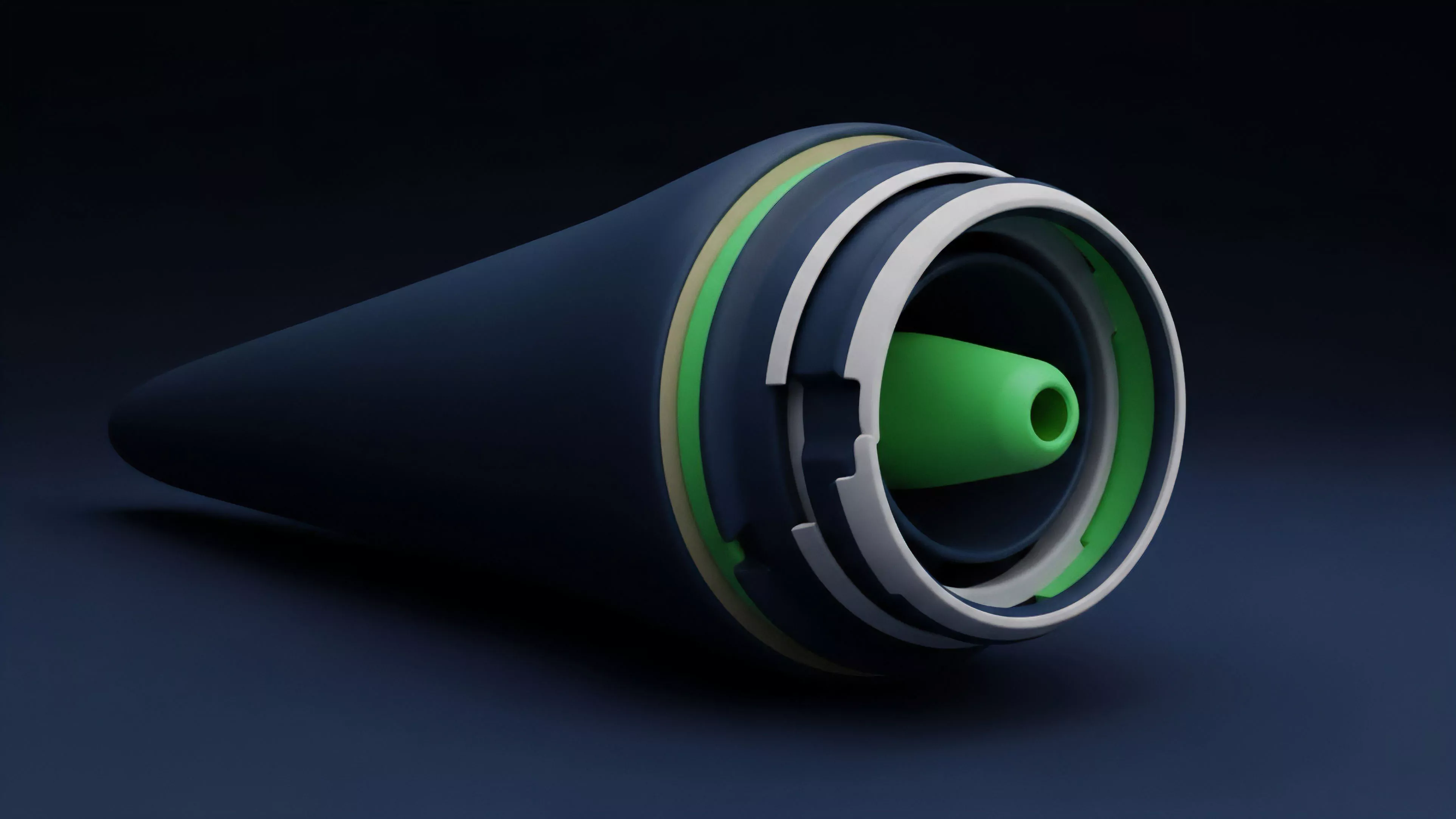

Proof Latency Optimization

Meaning ⎊ Proof Latency Optimization reduces the temporal gap between order submission and settlement to mitigate front-running and improve capital efficiency.

Cryptographic Proof Optimization

Meaning ⎊ Cryptographic Proof Optimization drives decentralized derivatives scalability by minimizing the on-chain verification cost of complex financial state transitions through succinct zero-knowledge proofs.

Cryptographic Proof Optimization Techniques

Meaning ⎊ Cryptographic Proof Optimization Techniques enable the succinct, private, and high-speed verification of complex financial state transitions in decentralized markets.

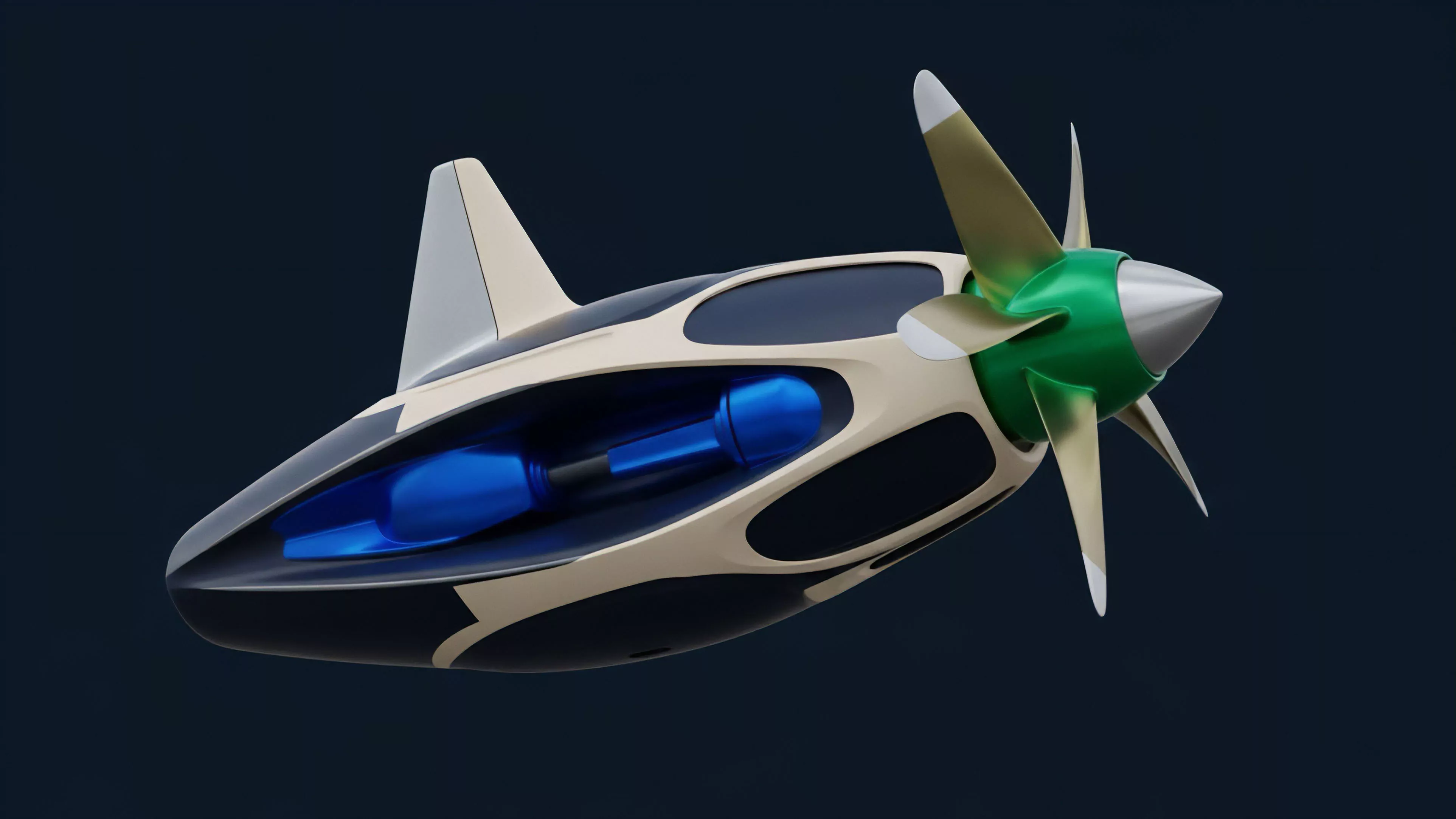

Transaction Processing Optimization

Meaning ⎊ Decentralized Atomic Settlement Layer (DASL) is a two-layer protocol that uses cryptographic proofs to achieve near-instantaneous, low-cost options transaction finality, significantly boosting capital efficiency and mitigating systemic liquidation risk.