Hardware Acceleration for ZK

Meaning ⎊ Using specialized hardware like GPUs or ASICs to optimize and speed up the intensive ZK-proof generation process.

Low Latency Hardware

Meaning ⎊ Low Latency Hardware provides the physical foundation for high-speed execution, enabling precise arbitrage and liquidity provision in digital markets.

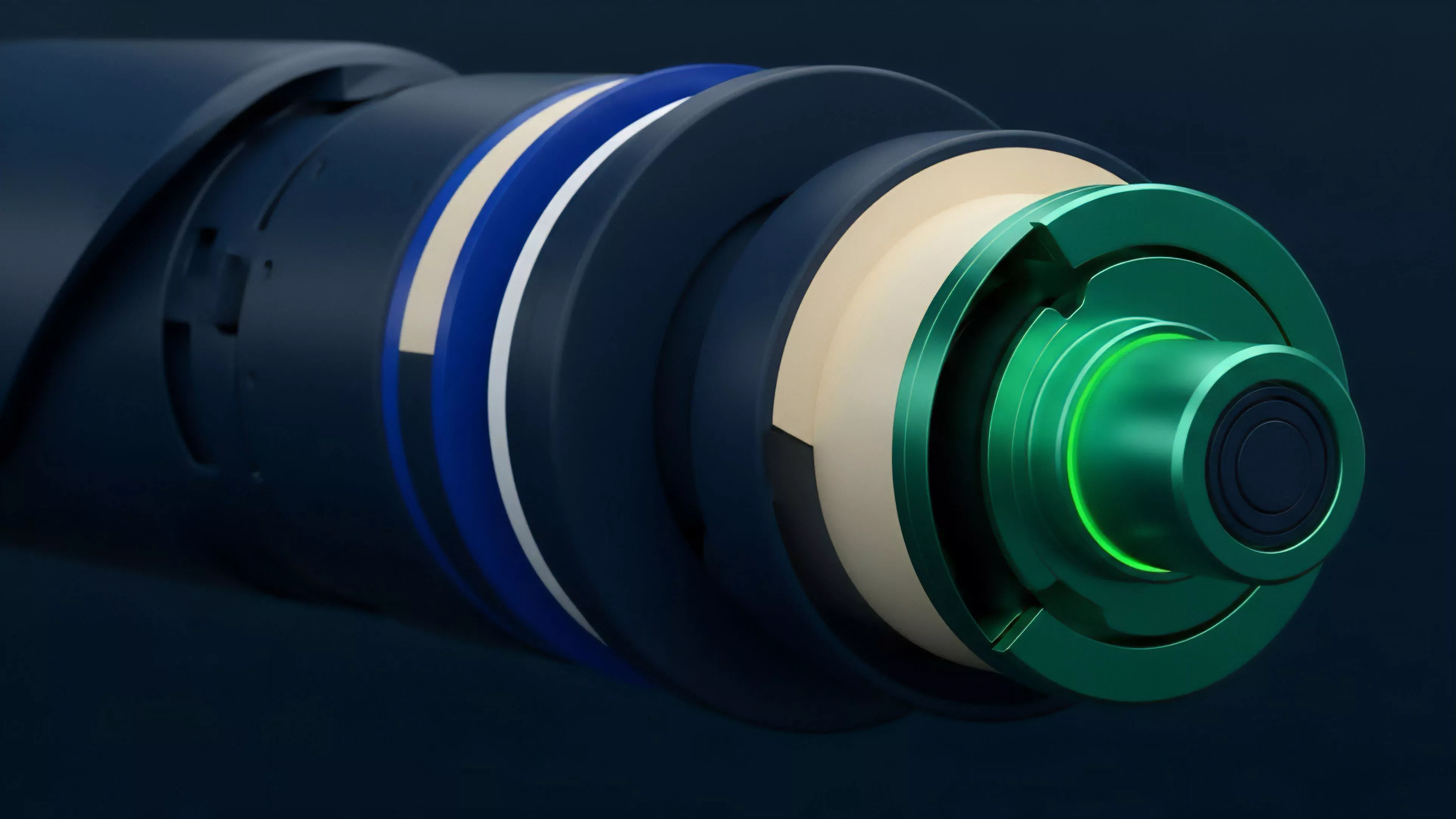

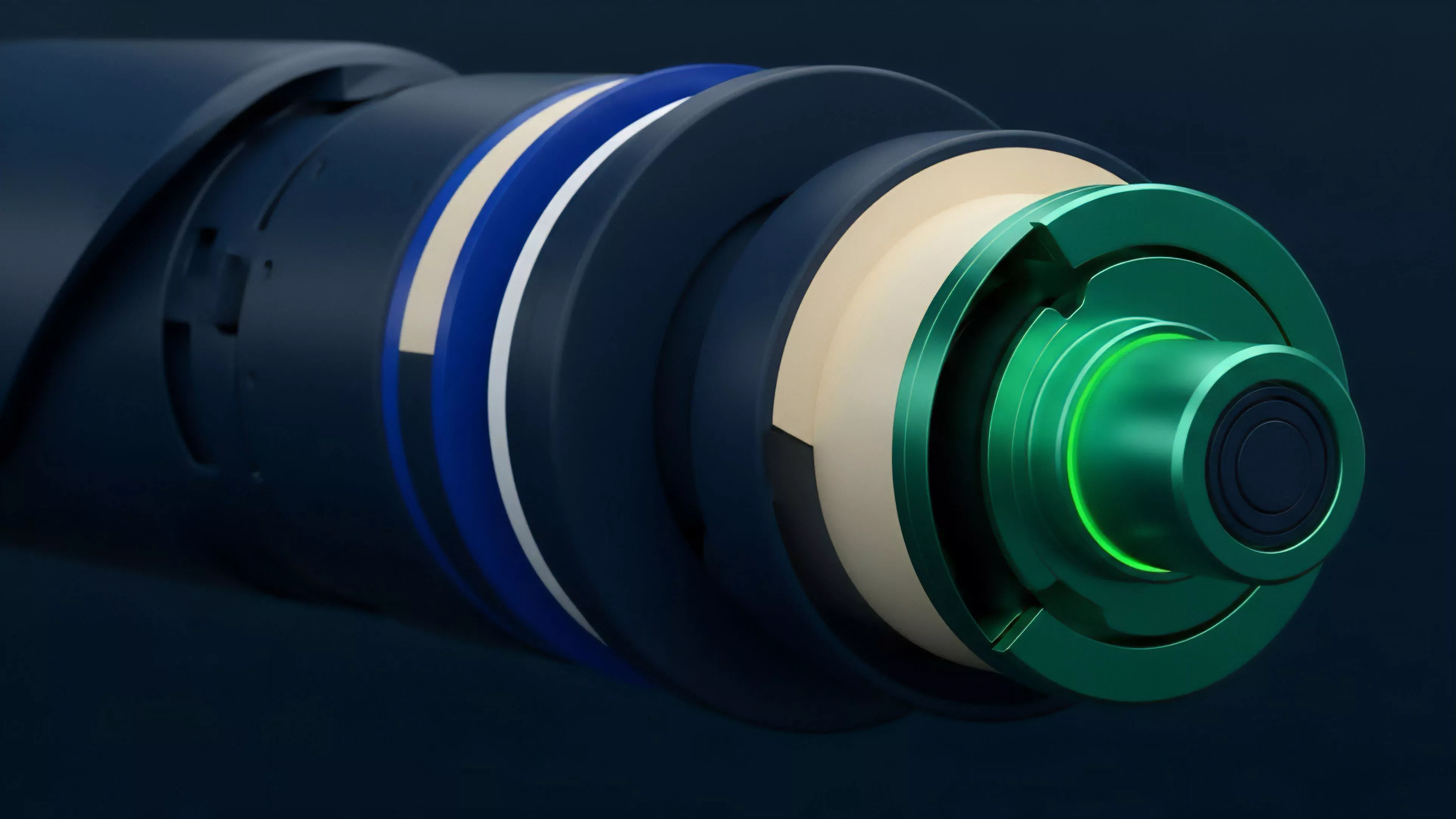

Hardware Resource Isolation

Meaning ⎊ Partitioning server resources to ensure that critical trading tasks are shielded from non-essential system activity.

NIC Hardware Acceleration

Meaning ⎊ Offloading network-related computational tasks to the network card hardware to free up CPU resources for trading logic.

Hardware Wallet Firmware

Meaning ⎊ The internal software of a hardware wallet that manages keys and signing, requiring strict verification for security.

Hardware Requirements for Nodes

Meaning ⎊ The technical specifications needed to run a network node and participate in consensus.

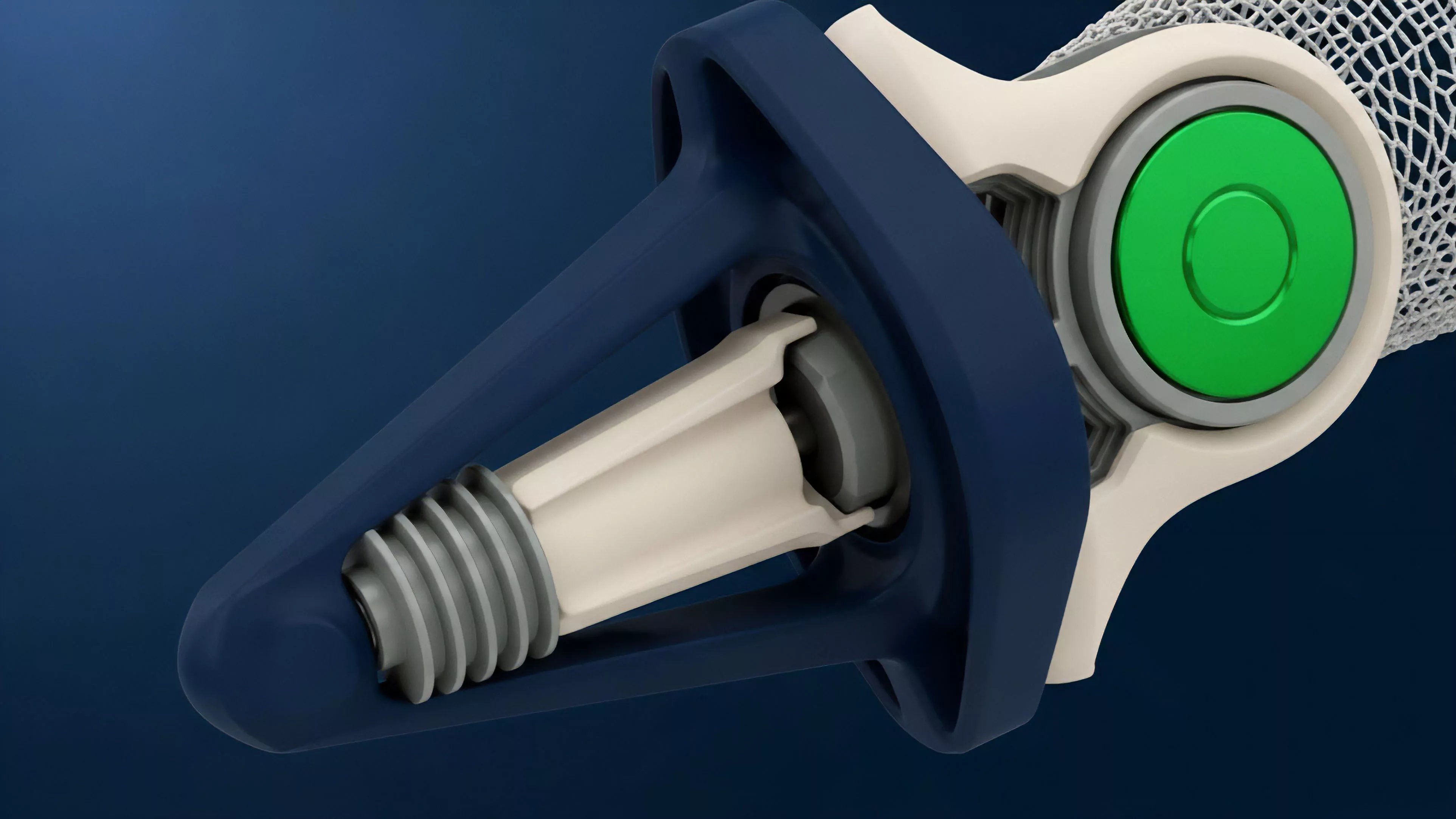

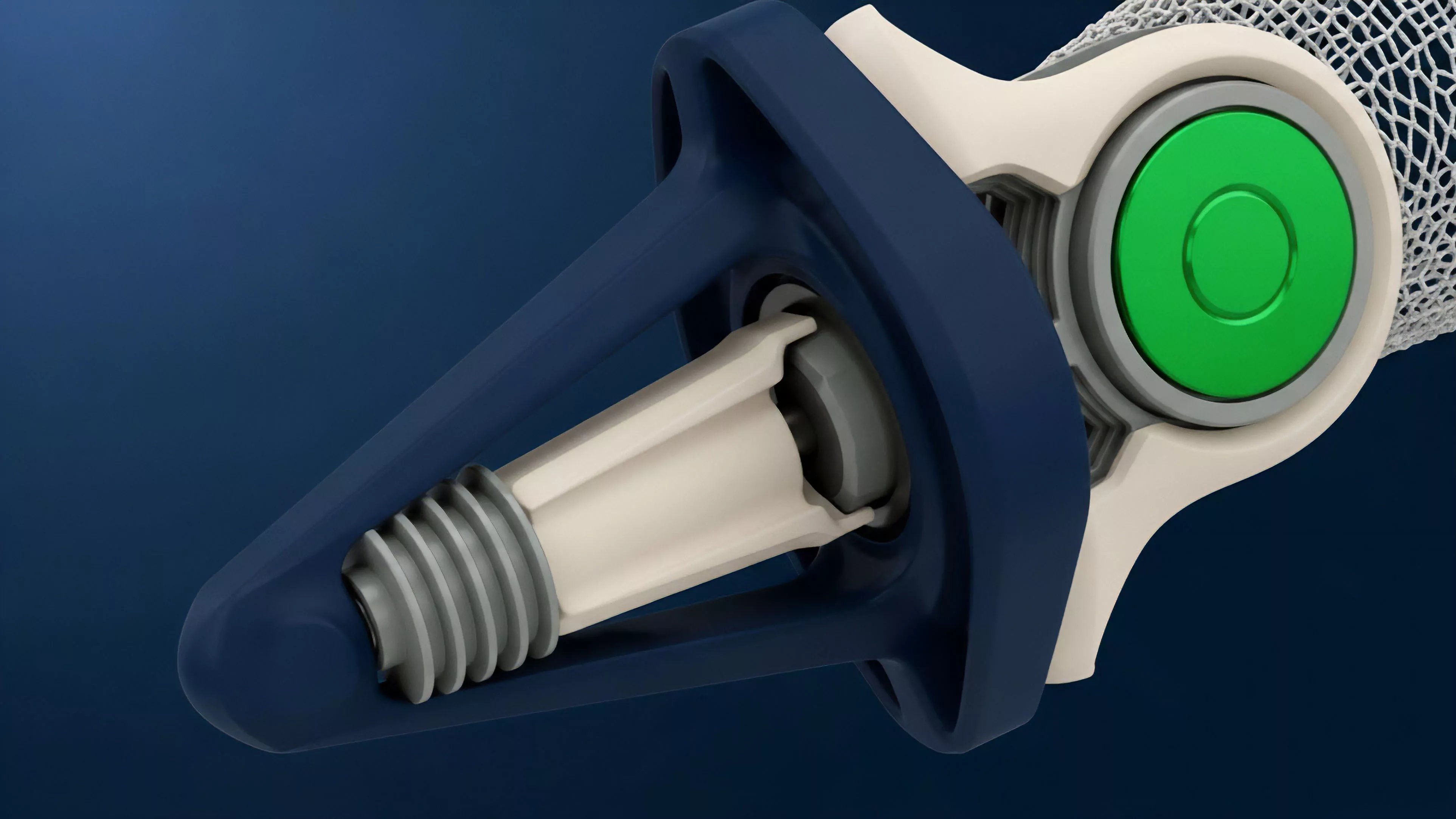

Tamper-Proof Hardware

Meaning ⎊ Tamper-Proof Hardware provides the immutable physical foundation required to secure cryptographic assets and automate trust in decentralized markets.

Hardware Security Testing

Meaning ⎊ Hardware security testing ensures the physical integrity of cryptographic devices, preventing key extraction that would compromise derivative settlement.

Trading Hardware Performance

Meaning ⎊ Speed and precision of computing systems used to execute financial orders and process market data with minimal latency.

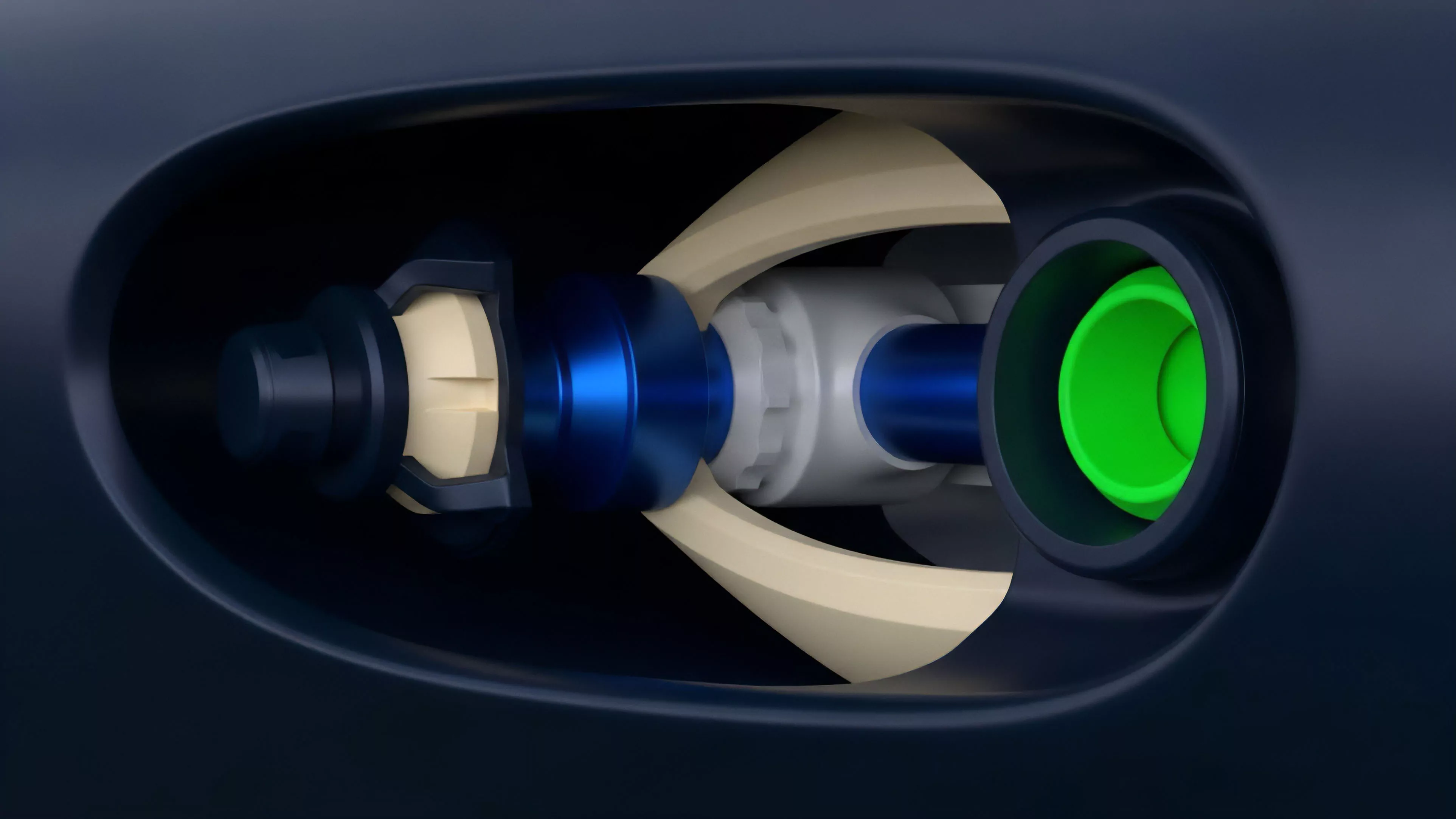

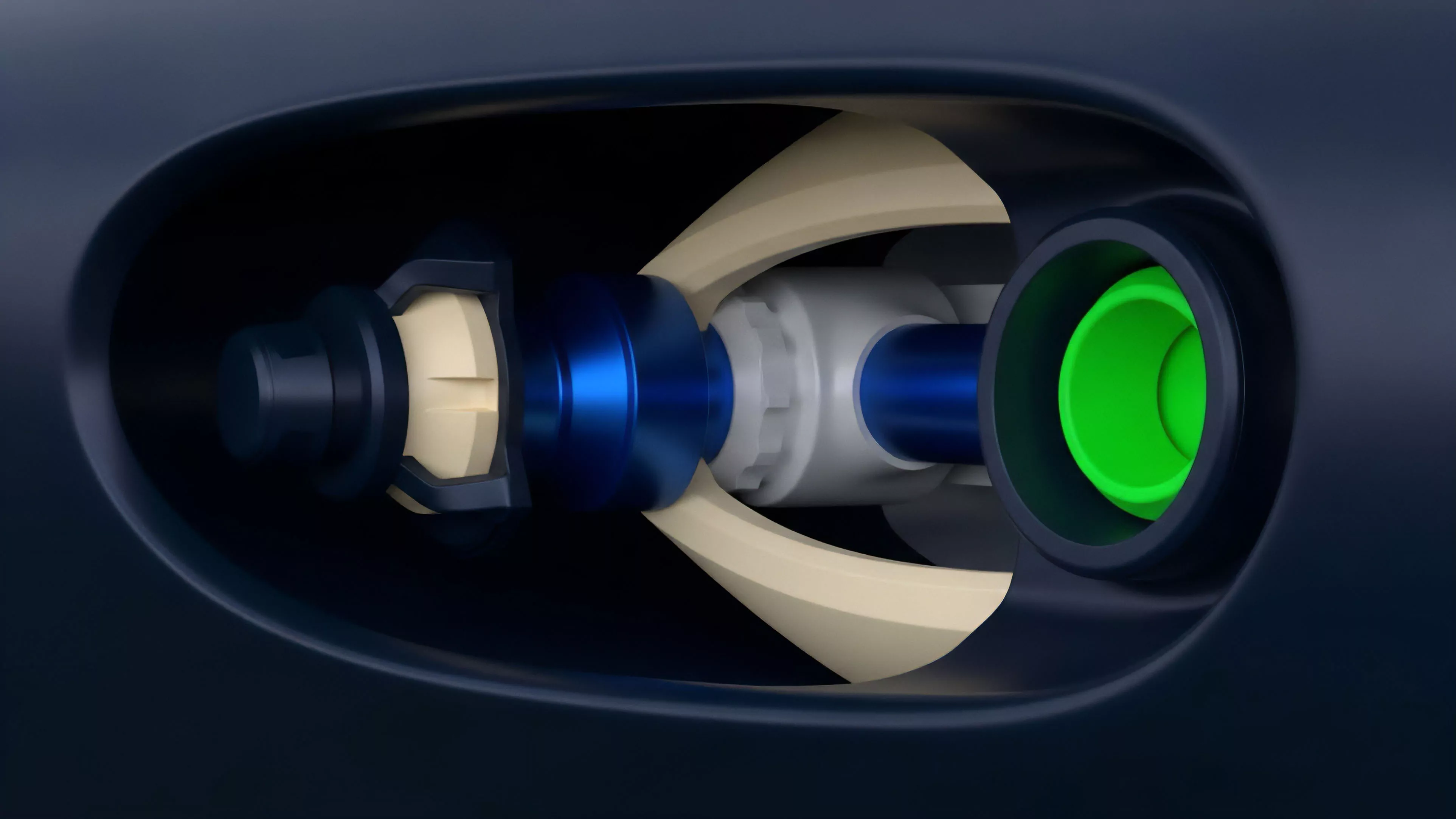

Prover Hardware Requirements

Meaning ⎊ The specific hardware specifications necessary to perform the computational task of generating proofs efficiently.

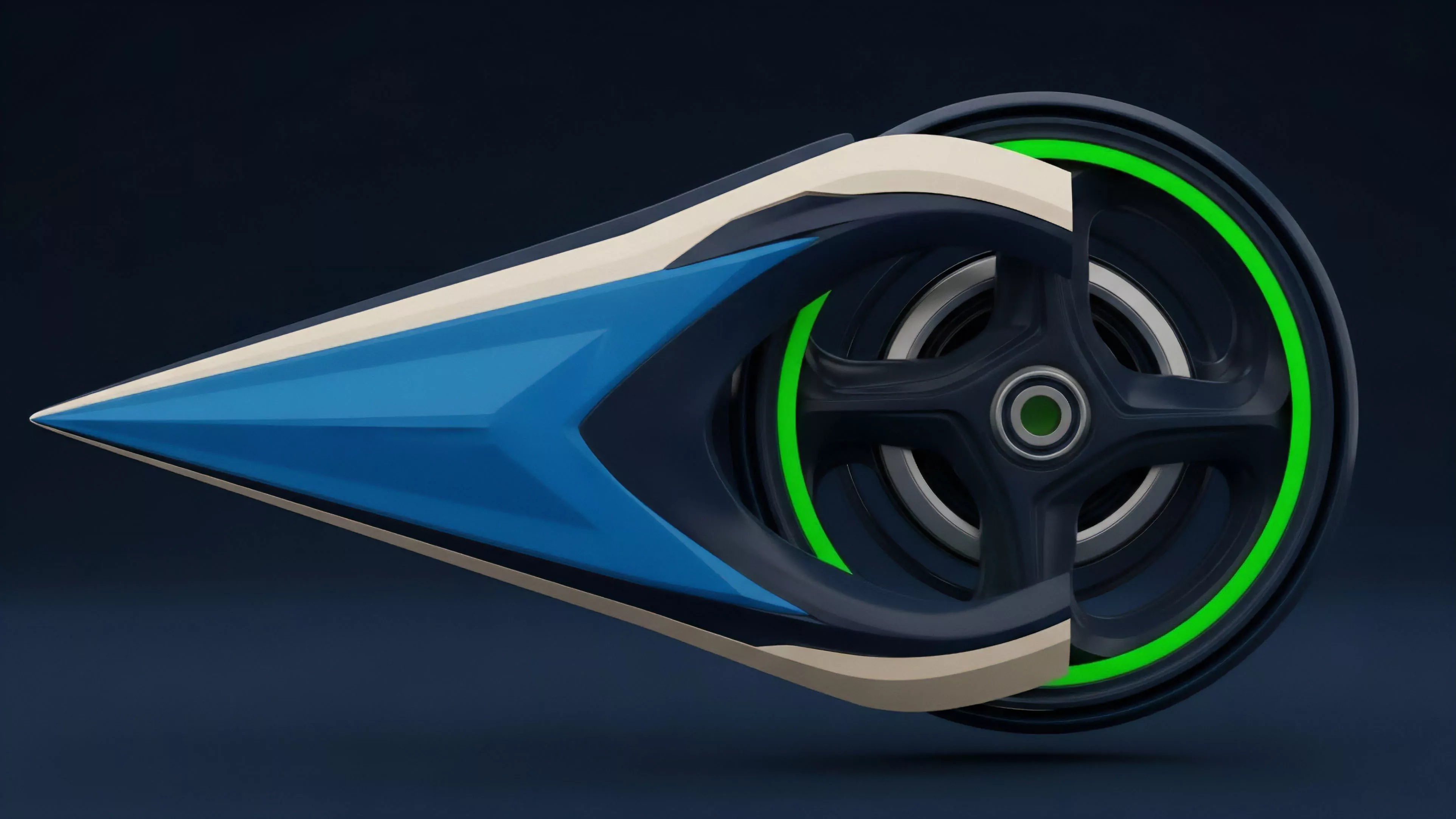

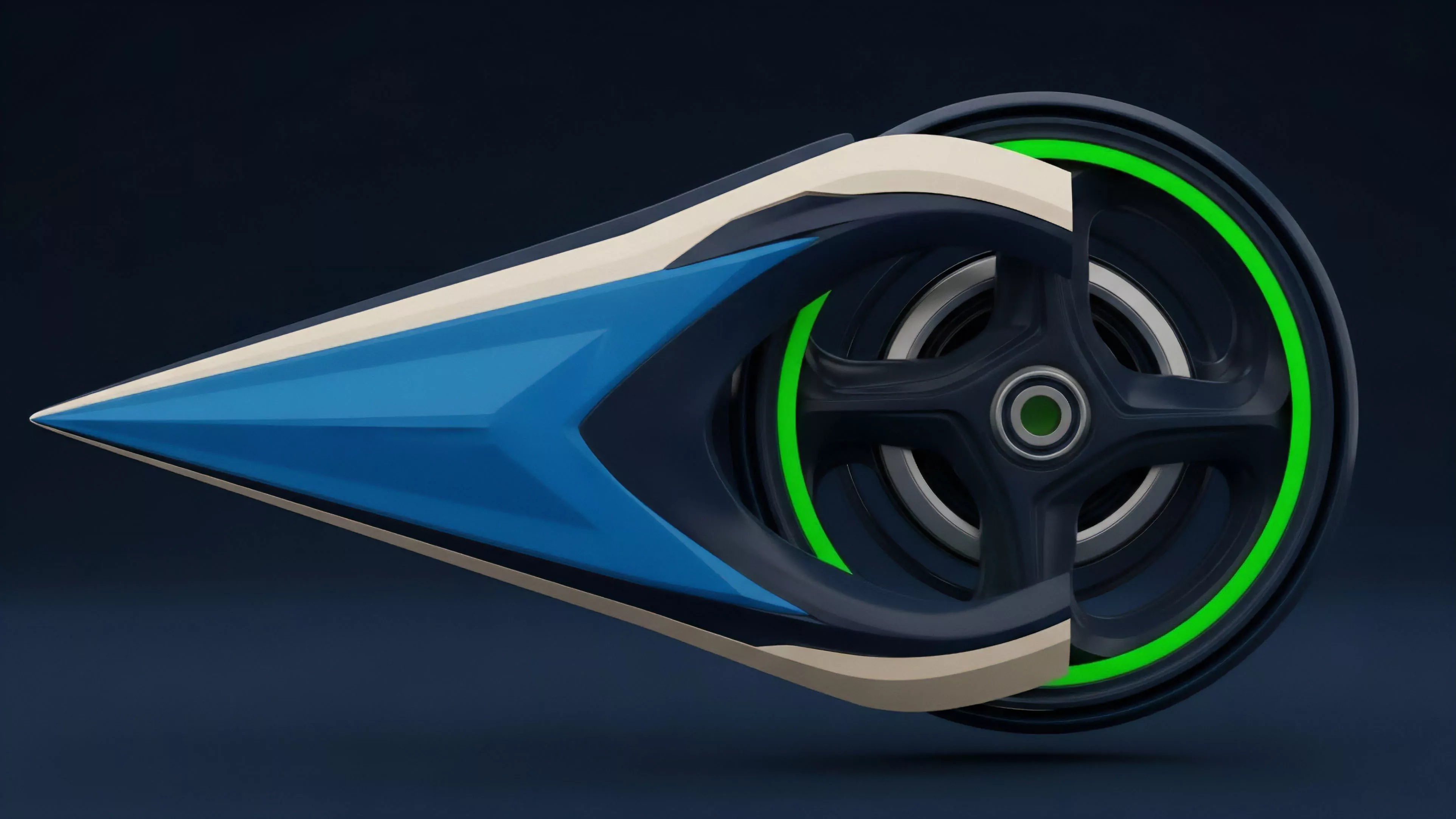

Hardware Acceleration for Provers

Meaning ⎊ Utilizing specialized hardware like ASICs or FPGAs to increase the speed of generating complex cryptographic proofs.

Multi-Stage Commit Processes

Meaning ⎊ Transaction patterns ensuring system-wide agreement on state changes through multiple verification stages before final commitment.