Essence

Hardware Security Testing represents the rigorous verification of physical cryptographic modules, secure enclaves, and trusted execution environments against both side-channel analysis and fault injection vectors. In the architecture of decentralized finance, these physical components function as the ultimate arbiters of private key integrity. When software-based defenses prove insufficient against sophisticated local or remote physical attacks, the security of high-value derivative positions relies entirely on the tamper-resistance of the underlying hardware substrate.

Hardware security testing validates the physical and logical boundaries protecting cryptographic material from unauthorized extraction or manipulation.

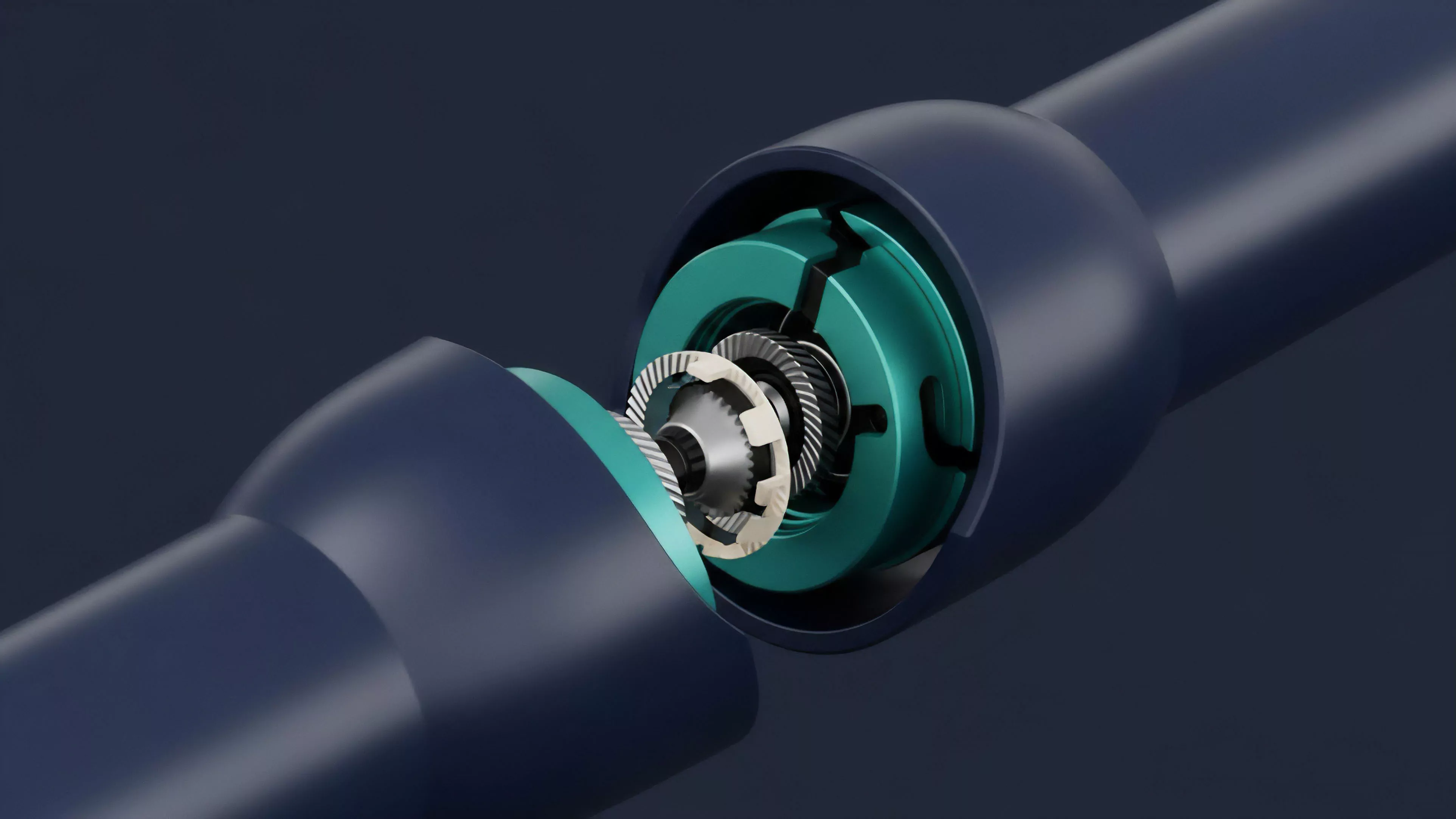

The discipline involves subjecting microcontrollers, secure elements, and hardware wallets to non-invasive and invasive stress tests. These procedures determine the resilience of a device against power analysis, electromagnetic emissions monitoring, and clock glitching. The systemic relevance becomes clear when considering the role of hardware in signing transactions for large-scale derivative settlement.

If the hardware component fails, the entire chain of trust governing the derivative contract collapses, leading to potential catastrophic loss of collateral.

Origin

The genesis of this field lies in the historical development of smart card security and the subsequent emergence of specialized cryptographic hardware. Early implementations of public-key infrastructure necessitated secure storage for sensitive keys, leading to the creation of the Hardware Security Module. These devices were originally designed for enterprise data centers to handle high-volume signing operations without exposing keys to general-purpose operating systems.

- Cryptographic Hardware Evolution moved from simple passive storage to active, tamper-responsive integrated circuits.

- Side-Channel Research identified that cryptographic algorithms leak information through physical power consumption patterns during execution.

- Fault Injection Techniques demonstrated that precise environmental disruptions could force faulty computations, revealing secret key bits.

As financial markets shifted toward decentralized ledger technology, the necessity for secure, user-verifiable key management accelerated. The transition from server-side security to individual, edge-based security shifted the burden of testing from centralized entities to developers and auditors of consumer-grade cryptographic hardware. This evolution mirrors the broader movement toward self-custody, where the responsibility for asset protection rests on the robustness of the physical security architecture.

Theory

The theoretical framework governing this domain relies on the adversarial modeling of physical systems.

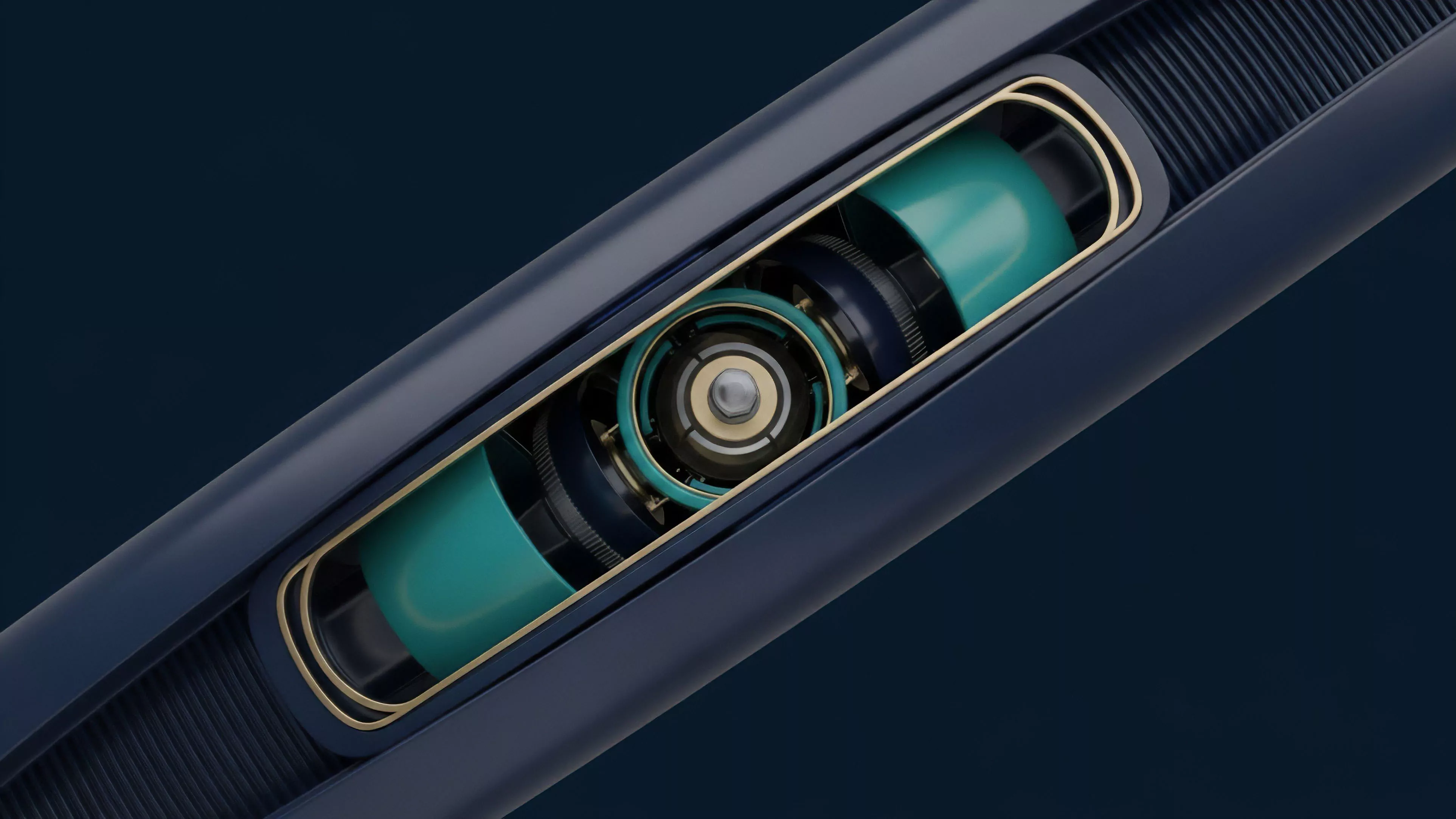

Unlike software environments where code execution is predictable, physical hardware operates within an analog domain subject to noise, temperature fluctuations, and electromagnetic interference. Analysts model these interactions using probabilistic frameworks to assess the difficulty of extracting sensitive data.

| Attack Vector | Physical Mechanism | Defensive Countermeasure |

| Differential Power Analysis | Correlation of power draw with secret key operations | Power masking and current randomization |

| Voltage Glitching | Intentional power supply instability | Active voltage monitoring and brown-out detection |

| Photonic Emission Analysis | Light emission during transistor switching | Opaque packaging and metal shielding layers |

The fundamental challenge involves the gap between theoretical security proofs and the physical implementation. Even mathematically sound cryptographic algorithms fail if the hardware execution path permits information leakage. Analysts apply information theory to quantify the number of traces required to successfully reconstruct a key, treating the hardware as a communication channel where the secret key is the signal and physical leakage is the noise.

The physical security of cryptographic assets depends on minimizing the correlation between internal state transitions and observable external physical phenomena.

Quantum mechanical effects sometimes enter this discourse, as the miniaturization of silicon processes reaches levels where electron tunneling and other phenomena impact security. The interplay between low-level transistor behavior and high-level financial risk creates a unique requirement for analysts who bridge the gap between solid-state physics and derivative risk management.

Approach

Current methodologies emphasize automated testing pipelines that simulate adversarial environments. Security engineers utilize specialized laboratory equipment to capture high-resolution power traces and manipulate clock frequencies while the device executes signing operations.

This data is then processed through statistical software to identify deviations that signify potential vulnerabilities.

- Baseline Profiling involves establishing the normal power consumption characteristics of a device during standard operations.

- Differential Analysis compares the baseline against traces captured during private key usage to isolate secret key dependencies.

- Fault Injection Simulation systematically tests the response of the device to environmental stress to observe if it fails securely or leaks data.

This approach demands a high level of technical precision, as even minor misalignments in timing can render an entire test suite invalid. The financial significance remains paramount, as these tests are performed on the very devices that secure the margin accounts of derivative traders. Any failure to identify a vulnerability at this stage introduces a systemic risk that cannot be mitigated by smart contract logic alone, as the breach occurs at the hardware level, completely bypassing the consensus mechanism.

Evolution

The field has moved from manual, artisanal testing to high-throughput, automated verification processes.

Early efforts focused on high-end enterprise equipment, whereas current efforts target mass-produced consumer hardware. This shift reflects the democratization of secure asset custody, where the hardware itself becomes the most accessible attack vector for sophisticated actors.

Hardware security testing is shifting from reactive post-production audits to proactive design-for-security paradigms in hardware manufacturing.

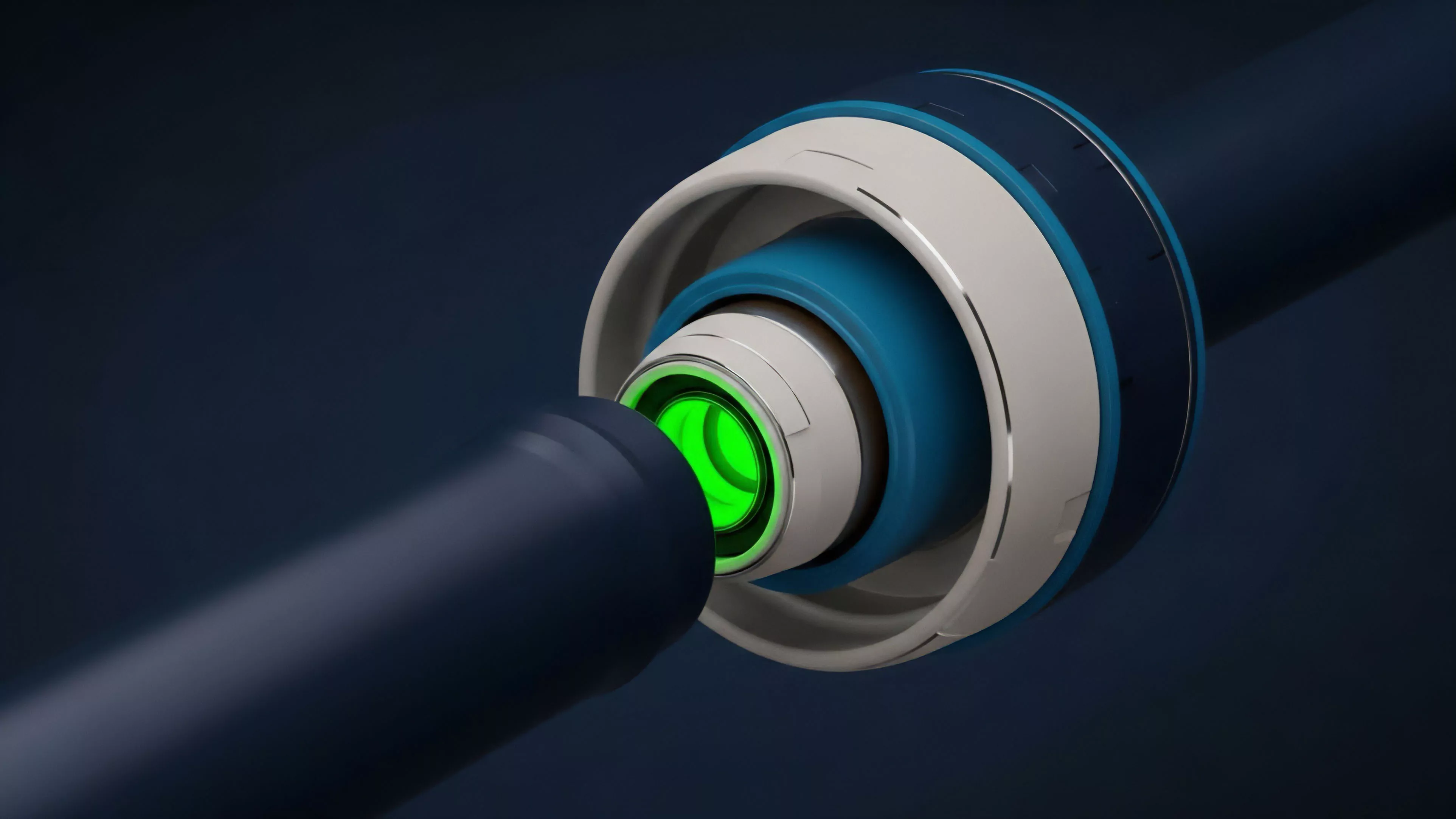

The integration of Secure Elements into mobile devices and general-purpose hardware has increased the scope of required testing. Furthermore, the rise of Trusted Execution Environments allows for more complex, software-defined hardware security, complicating the testing process by blurring the line between physical and logical security. The complexity of modern system-on-chip architectures necessitates a holistic view, where hardware and software are tested as an integrated, inseparable unit.

Horizon

The future of this discipline points toward the adoption of formal verification methods applied to physical hardware descriptions.

By mathematically proving that the hardware design cannot exhibit certain leakage patterns, the industry aims to move beyond the limitations of empirical testing. This represents a significant shift toward proactive security, where the physical architecture is inherently resistant to known attack vectors by design.

- Formal Hardware Verification will likely become the standard for critical financial infrastructure to ensure physical integrity.

- Automated Side-Channel Mitigation will be embedded at the silicon level, rendering traditional power analysis techniques ineffective.

- Hardware-Based Zero Knowledge Proofs will enable secure computation without requiring the underlying hardware to be perfectly shielded.

As decentralized markets mature, the integration of hardware security testing into the standard auditing process for financial protocols will be required. The inability to verify the physical security of the signing mechanism will eventually be viewed as a critical failure in the due diligence process for institutional participation in decentralized derivative markets. The next frontier involves the development of self-attesting hardware that can provide cryptographic proof of its own physical integrity during the transaction signing process. What paradoxes arise when the pursuit of absolute physical security through hardware design inadvertently creates new, opaque failure points that are beyond the reach of conventional auditing?