Essence

Low Latency Hardware functions as the physical substrate for high-frequency financial execution within decentralized order books and derivative venues. It minimizes the temporal gap between signal reception, order generation, and on-chain or off-chain settlement. By optimizing the path from market data ingestion to packet transmission, this infrastructure determines the viability of arbitrage strategies and market-making operations.

The physical performance of trading infrastructure dictates the competitive threshold for capturing arbitrage opportunities in fragmented digital asset markets.

Architecturally, this involves specialized components designed to bypass standard operating system bottlenecks. Key elements include:

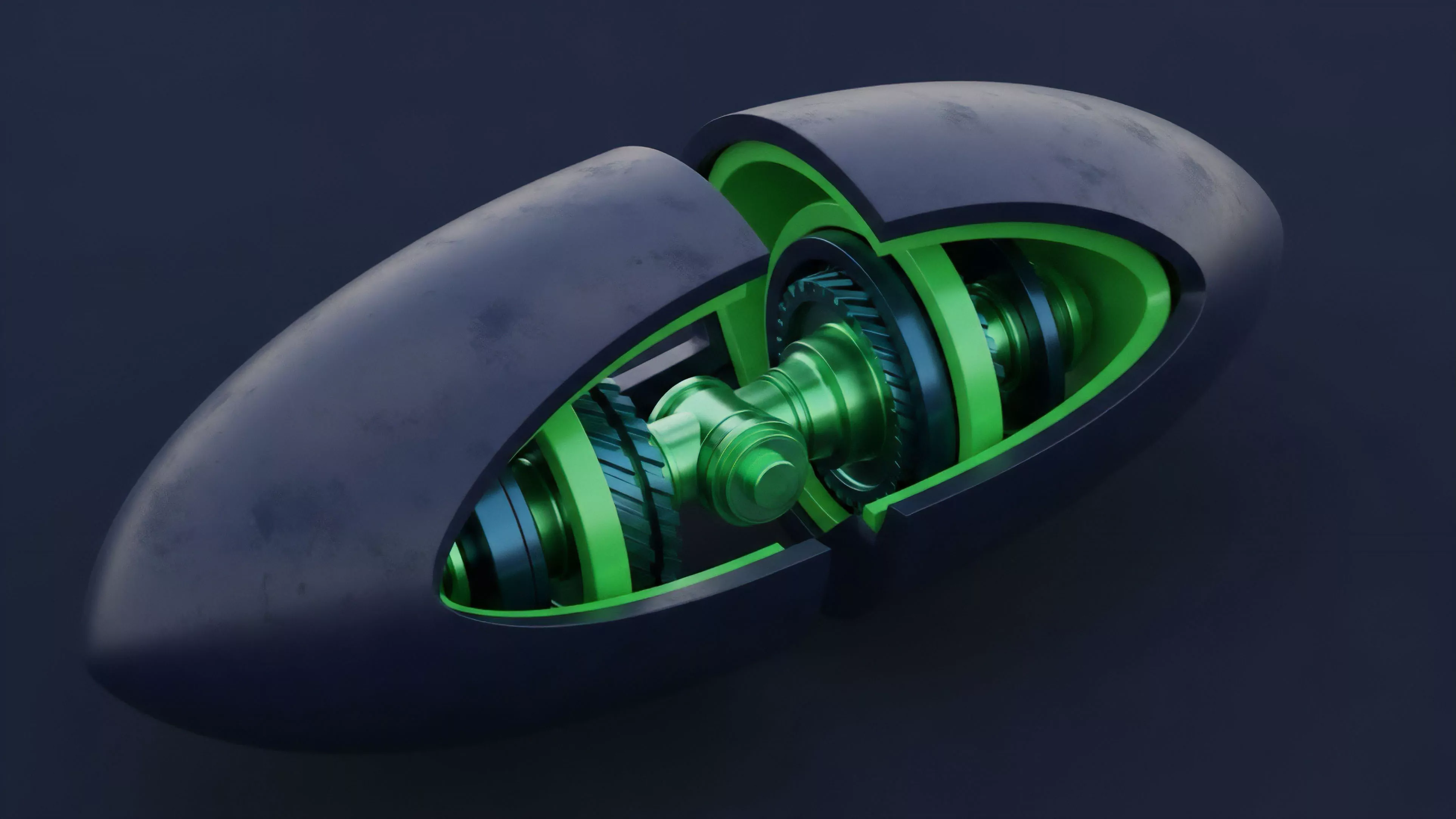

- Field Programmable Gate Arrays which allow for hardware-level execution of trading logic, drastically reducing jitter compared to software-based engines.

- Network Interface Cards engineered for kernel bypass, ensuring direct memory access to incoming market data feeds.

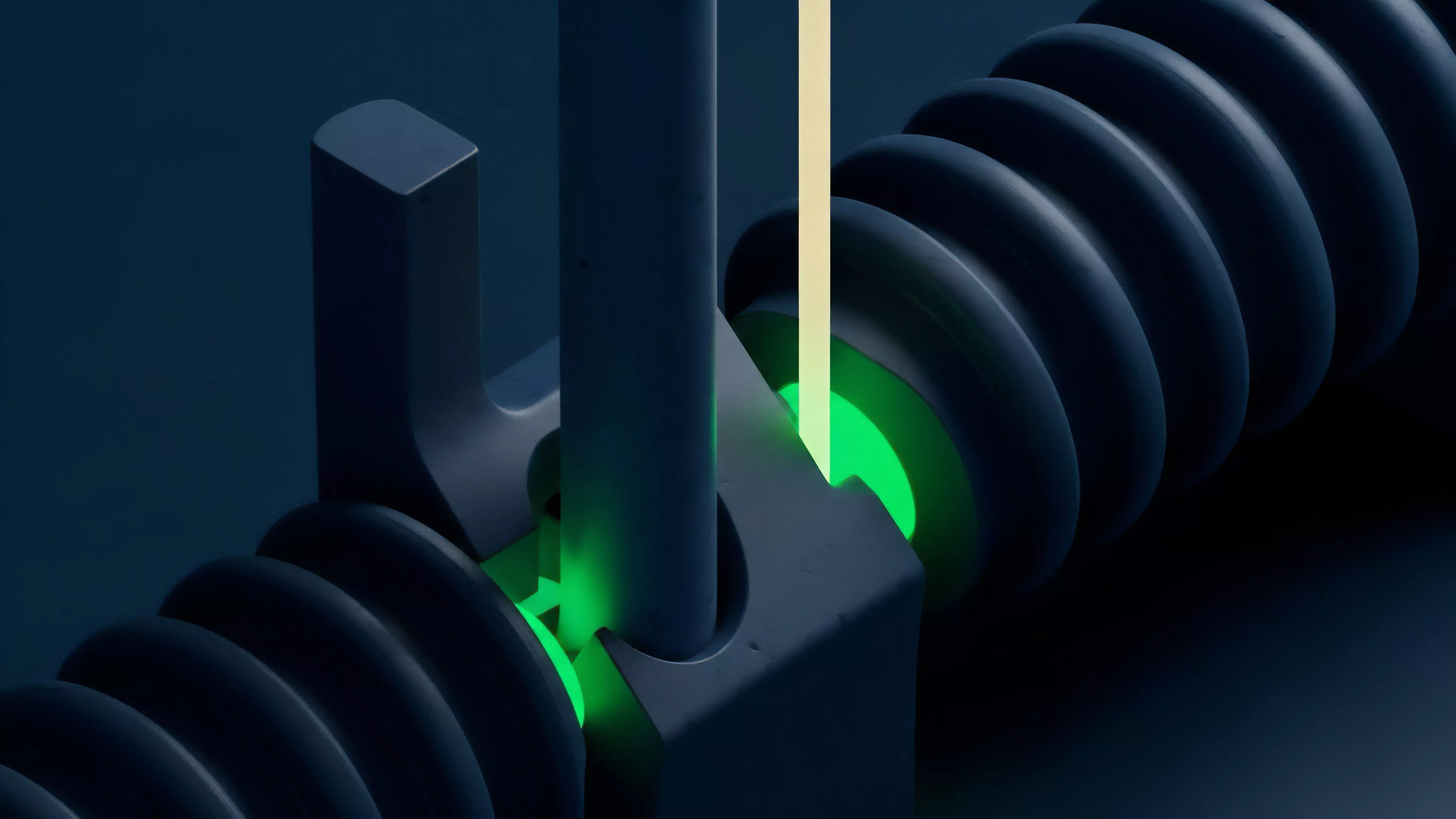

- Precision Time Protocol hardware synchronization, which provides the sub-microsecond timestamping necessary for sequencing transactions in adversarial environments.

This hardware exists to neutralize the inherent latency of distributed networks, where information propagation speed becomes the primary variable for profit accrual.

Origin

The pursuit of speed in financial markets originates from the fundamental asymmetry of information arrival. Early electronic trading platforms exposed the limitations of general-purpose computing, driving a transition toward custom silicon. Crypto markets inherited these architectural requirements but added the unique complexity of consensus-driven settlement.

Initial iterations relied on high-performance servers running optimized software stacks. However, the move toward decentralized exchanges created a new demand for hardware that could interface directly with protocol-level events. Developers began adapting Low Latency Hardware from traditional finance to handle the specific requirements of public blockchains, focusing on the reduction of processing overhead for cryptographic signing and transaction propagation.

Custom hardware design emerged from the necessity to collapse the execution timeline, turning microscopic speed advantages into significant capital efficiency.

This evolution shifted from optimizing internal matching engines to optimizing the connectivity between the liquidity provider and the protocol’s entry point. The history of this domain reflects a constant compression of time, moving from milliseconds to microseconds, as participants realized that in decentralized systems, the first agent to reach the mempool captures the arbitrage surplus.

Theory

The structural integrity of a trading system depends on the deterministic nature of its hardware path. Low Latency Hardware operates on the principle of minimizing jitter ⎊ the variance in packet arrival times ⎊ which is as critical as absolute speed.

In crypto derivatives, where liquidation events are triggered by rapid price movements, consistent performance allows for the precise management of delta-neutral portfolios. The mathematical model for hardware performance often focuses on the Tick to Trade duration. This is the interval between the arrival of a market data packet at the network interface and the departure of the corresponding order packet.

| Component | Function | Impact on Latency |

|---|---|---|

| FPGA | Logic Execution | Nanosecond-scale processing |

| Kernel Bypass | Data Path | Eliminates OS interrupt overhead |

| Atomic Clocks | Timestamping | Enables precise event sequencing |

The interaction between hardware and protocol physics is adversarial. Blockchain validators may prioritize transactions based on gas fees or specific ordering rules, forcing hardware architects to design systems that anticipate and adapt to these network-level behaviors. The system is a closed loop where the hardware must constantly re-calibrate to the changing congestion patterns of the underlying chain.

Sometimes, one considers the influence of quantum mechanics on hardware design ⎊ specifically, the physical limits of signal transmission speeds in copper and fiber ⎊ which serves as the ultimate, unyielding boundary for these systems. Anyway, returning to the core logic, the efficiency of this hardware dictates the success of automated market makers.

Approach

Current implementation of Low Latency Hardware centers on building private, optimized pathways to centralized and decentralized venues. Participants deploy co-located hardware clusters as close to the matching engine or validator nodes as physically possible.

This proximity reduces the propagation delay that would otherwise allow competitors to front-run or sandwich orders.

Hardware-level execution transforms abstract trading strategies into deterministic, high-probability outcomes within competitive digital asset venues.

The strategic deployment involves:

- Hardware Acceleration using programmable logic to handle the high throughput of WebSocket and FIX streams.

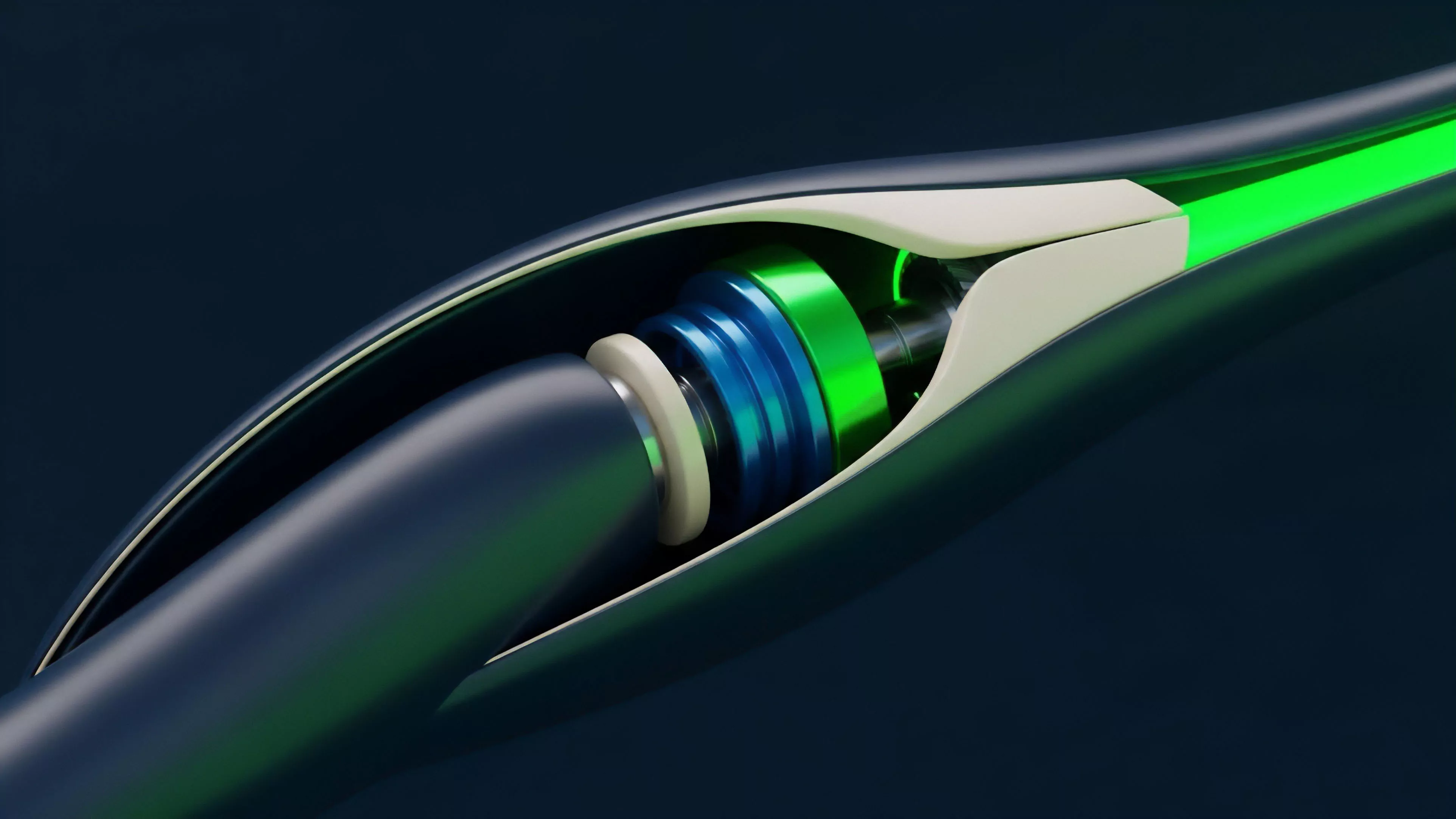

- Optimized Network Topology utilizing microwave or laser links to gain an edge in geographic latency.

- Deterministic Execution Engines that strip away non-essential processes, ensuring the hardware remains focused on order flow management.

The professional stake here is total. Any microsecond of delay in a volatile market translates into a direct loss of alpha, as the pricing models for options ⎊ particularly those involving complex greeks ⎊ become obsolete if the underlying asset price shifts before the hedge is executed.

Evolution

The journey of Low Latency Hardware has shifted from general-purpose server optimization to highly specialized, application-specific integrated circuits. Early participants utilized overclocked CPUs and standard network cards, but the intensity of competition in crypto derivative markets quickly rendered these obsolete.

The focus moved toward massive parallelization and the migration of trading logic into the silicon itself. This evolution is driven by the increasing complexity of on-chain derivatives, where the cost of interaction with smart contracts necessitates highly efficient transaction construction. Current architectures emphasize the ability to handle bursts of market activity without degrading the performance of the order execution loop.

| Phase | Primary Focus | Infrastructure |

|---|---|---|

| Generation 1 | Software Tuning | Standard Servers |

| Generation 2 | Network Optimization | Kernel Bypass NICs |

| Generation 3 | Hardware Logic | FPGA/ASIC Integration |

The current state reflects a maturing industry where the hardware is no longer a peripheral concern but the foundation of the firm’s competitive position. Firms that fail to invest in these specialized layers find themselves consistently providing liquidity to more agile, hardware-optimized agents.

Horizon

The future of Low Latency Hardware lies in the integration of artificial intelligence and machine learning directly into the hardware layer. This will enable real-time risk assessment and strategy adjustment at the speed of the incoming data stream, without the need for host-level intervention.

Furthermore, the development of hardware-accelerated cryptographic proof generation will allow for faster settlement on ZK-rollups and other scaling solutions.

Future hardware architectures will merge predictive modeling with execution, collapsing the gap between strategy formulation and market impact.

The next frontier involves the creation of hardware-defined protocols where the consensus rules are enforced by the physical properties of the network infrastructure itself. This will move beyond mere speed, focusing on the reliability and security of execution in increasingly hostile, automated markets. As these systems become more sophisticated, the distinction between the trader and the hardware will blur, resulting in autonomous entities that optimize their own physical performance to survive in the digital asset landscape.