Essence

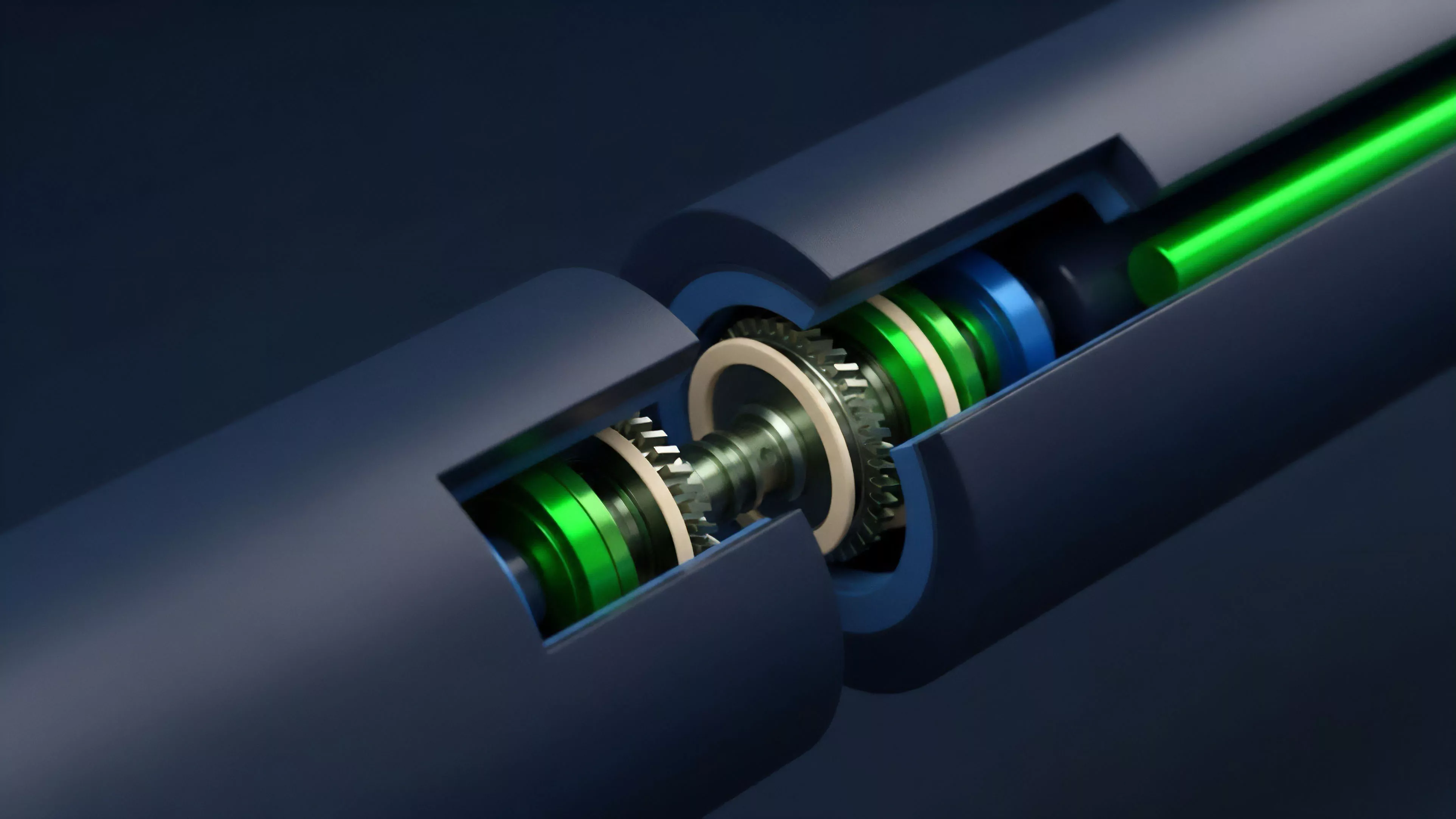

Tamper-Proof Hardware constitutes the physical bedrock upon which trustless financial systems operate. These specialized devices, ranging from Hardware Security Modules to Trusted Execution Environments, provide isolated computational environments where cryptographic keys and sensitive logic reside, protected from both external physical access and compromised software environments. The primary function involves ensuring that the execution of code ⎊ specifically, signing transactions or managing private key shards ⎊ occurs within a verified, immutable boundary, preventing unauthorized modification or extraction.

Tamper-Proof Hardware serves as the physical root of trust, isolating sensitive cryptographic operations from potentially hostile software environments.

These systems transform the abstract security guarantees of cryptography into tangible, enforced reality. Without this hardware layer, the security of digital assets remains vulnerable to memory scraping, side-channel attacks, and administrative malfeasance within centralized infrastructure. By embedding security at the silicon level, these components force adversarial agents to overcome physical barriers, shifting the cost-benefit analysis of an attack beyond the reach of rational actors.

Origin

The historical trajectory of Tamper-Proof Hardware originates in the evolution of cryptographic processing and the necessity for secure key management in institutional banking.

Early iterations were massive, proprietary Hardware Security Modules designed to safeguard the integrity of payment rails. As digital assets emerged, the focus shifted toward decentralized applications, necessitating a bridge between rigid, centralized security standards and the fluid, permissionless nature of blockchain networks.

- Hardware Security Modules originated as proprietary, air-gapped appliances designed for enterprise-grade key storage and high-speed cryptographic processing.

- Trusted Execution Environments emerged as secure, isolated CPU regions, enabling trusted code execution on commodity hardware.

- Secure Elements developed as specialized chips found in mobile devices, providing the hardware-backed storage required for personal wallet security.

This transition reflects a broader architectural movement from perimeter-based security to data-centric, hardware-enforced protection. The design philosophy moved away from monolithic, proprietary black boxes toward modular, interoperable hardware architectures capable of sustaining the requirements of decentralized finance protocols and sovereign identity management.

Theory

The theoretical framework governing Tamper-Proof Hardware centers on the principle of physical isolation. By creating a distinct, hardened environment, the device ensures that sensitive operations occur independently of the host operating system.

This isolation relies on cryptographic attestation, where the device provides verifiable proof that the code currently executing is identical to the authorized, untampered firmware.

| Component | Security Mechanism | Primary Function |

|---|---|---|

| Secure Element | Physical anti-tamper mesh | Isolated key storage |

| Trusted Execution Environment | CPU-level memory encryption | Secure code execution |

| Hardware Security Module | FIPS-validated physical enclosure | Enterprise-grade signing |

The mathematical rigor here involves ensuring that even with total control over the operating system, an attacker cannot extract private key material or influence the outcome of the signing process. The hardware enforces access control policies that are hardcoded into the silicon, rendering the logic resistant to software-based privilege escalation or remote exploitation.

Physical isolation ensures that cryptographic secrets remain unreachable even when the host operating system faces total compromise.

This domain also intersects with game theory, as the cost of physical intrusion ⎊ requiring specialized laboratory equipment and significant time ⎊ must exceed the potential value of the assets stored within. The design goal is to make the hardware an economic obstacle rather than a mere technical one.

Approach

Current implementation strategies for Tamper-Proof Hardware prioritize the integration of secure enclaves within decentralized protocols. Developers now deploy sophisticated multi-party computation schemes where private keys are never held in a single device, but instead fragmented across multiple, geographically distributed hardware modules.

This architecture minimizes the impact of a single device failure or compromise.

- Remote Attestation enables users to verify the integrity of the hardware environment before initiating any sensitive transaction.

- Multi-Party Computation distributes key shards across different hardware devices, eliminating single points of failure.

- Physical Unclonable Functions utilize unique silicon-level manufacturing variations to create hardware-bound identities that cannot be replicated.

Market participants now utilize these mechanisms to facilitate institutional-grade custody, where the signing process is bound by strict, hardware-enforced rules regarding transaction limits, authorized destinations, and temporal constraints. This approach effectively moves the risk management layer from the human decision-making process into the deterministic, immutable logic of the hardware.

Evolution

The transition from legacy hardware appliances to modern, developer-friendly hardware interfaces marks the most significant shift in the utility of Tamper-Proof Hardware. Early implementations were restricted to high-frequency traders and institutional custodians.

Today, open-source standards and standardized hardware interfaces have democratized access, allowing protocol developers to build hardware-backed security directly into decentralized applications.

Hardware-backed security has transitioned from a specialized institutional tool to a foundational requirement for decentralized protocol integrity.

The evolution also highlights a shift toward hybrid models, where software-defined security and hardware-enforced security operate in tandem. This creates a layered defense, where software logic handles flexibility and scalability, while the hardware provides the immutable, non-repudiable foundation for transaction signing. This development reflects a maturation of the ecosystem, where the focus has moved toward resilience and the mitigation of systemic contagion risks.

Horizon

The future of Tamper-Proof Hardware lies in the convergence of confidential computing and zero-knowledge proofs.

This development will allow protocols to process sensitive financial data ⎊ such as order flow and private positions ⎊ within secure enclaves while generating cryptographic proofs of correctness for the broader network. The integration of hardware-bound identities with decentralized identity frameworks will further enhance the security of sovereign financial interactions.

| Future Trend | Technical Driver | Market Impact |

|---|---|---|

| Confidential Computing | CPU-level memory encryption | Privacy-preserving decentralized finance |

| Zero-Knowledge Hardware | Hardware-accelerated proving | Scalable, private transaction settlement |

| Decentralized Hardware | Hardware-verified incentive layers | Resilient, distributed trust networks |

The trajectory points toward hardware that is increasingly invisible, integrated directly into the infrastructure of decentralized markets. As the industry matures, the distinction between hardware and software security will blur, resulting in systems that are fundamentally secure by design rather than through reactive patching. The ultimate goal is a global, decentralized financial operating system where the integrity of every transaction is guaranteed by the physical laws of the underlying hardware. What paradox emerges when the pursuit of absolute physical security creates new, centralized dependencies on the few manufacturers of specialized silicon?