Essence

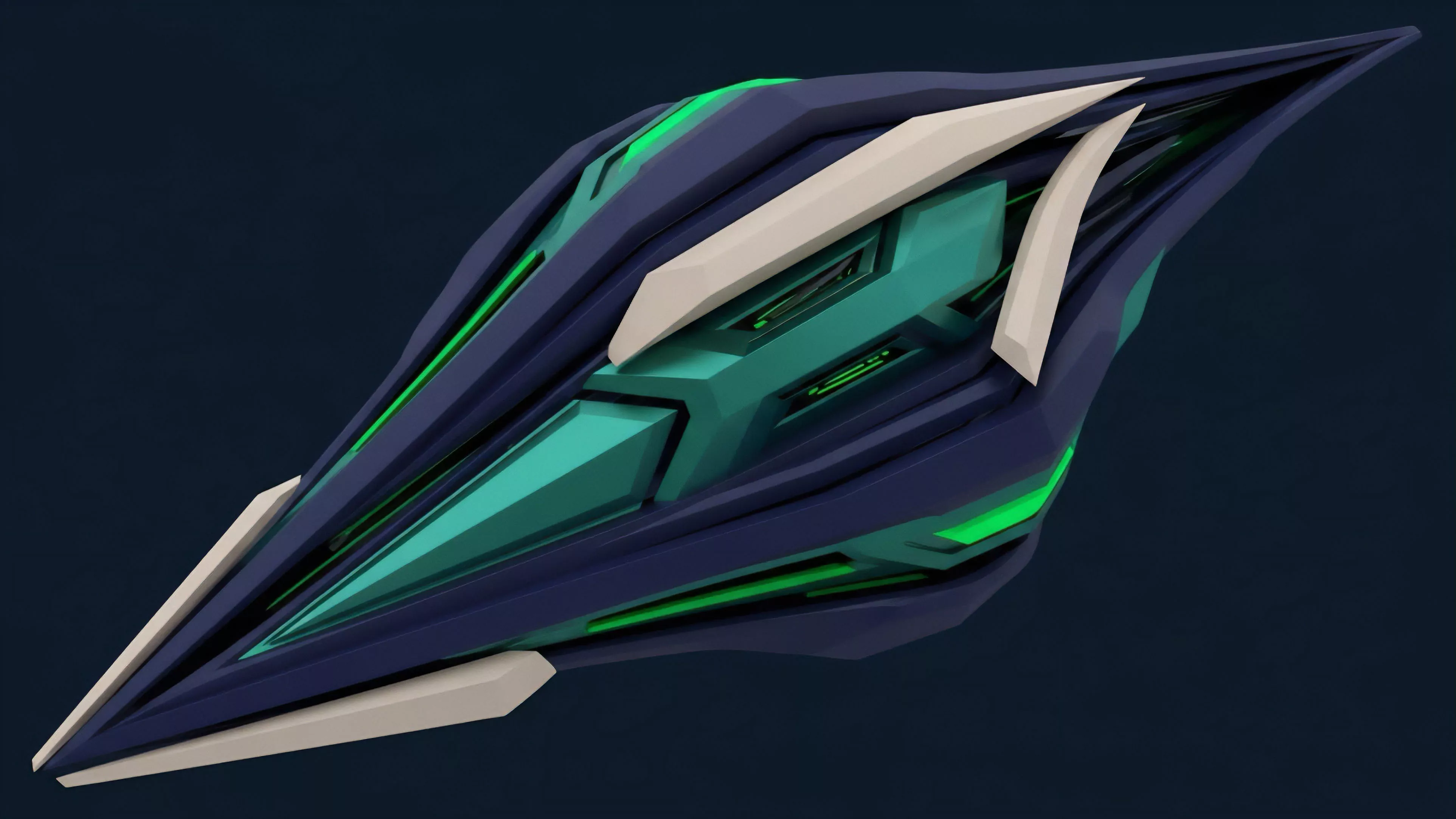

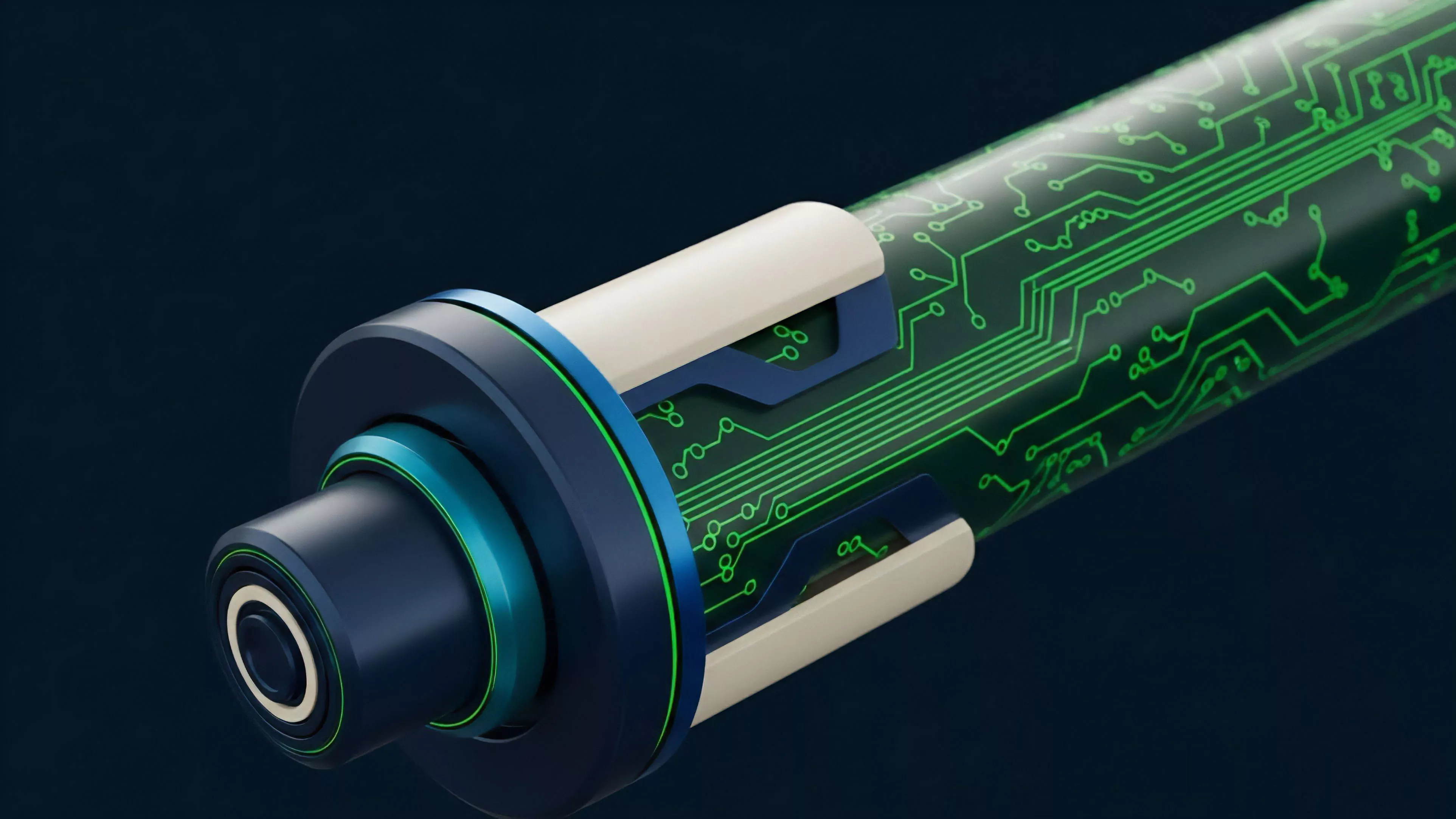

Zero-Knowledge Hardware represents the physical acceleration layer for cryptographic proof generation. These specialized computational units, typically manifested as Field Programmable Gate Arrays or Application-Specific Integrated Circuits, optimize the execution of resource-intensive mathematical operations required to generate non-interactive zero-knowledge proofs. By offloading heavy polynomial commitment schemes and multi-scalar multiplications from general-purpose processors, these systems reduce the latency of state verification within decentralized networks.

Zero-Knowledge Hardware functions as the dedicated computational substrate for generating cryptographic proofs, enabling scalable and private state transitions.

This architectural specialization solves the primary bottleneck in privacy-preserving finance. Without dedicated hardware, the computational cost of creating proofs for complex transactions limits throughput and increases the financial burden on participants. By integrating these units into the infrastructure stack, protocols achieve performance parity with centralized clearing houses while maintaining decentralized security guarantees.

Origin

The genesis of Zero-Knowledge Hardware traces back to the computational complexity inherent in zk-SNARKs and zk-STARKs.

Early cryptographic implementations relied upon standard CPU-based execution, which proved insufficient for real-time financial settlement. As protocols sought to increase transaction volume, the industry pivoted toward specialized hardware designs inspired by the trajectory of Bitcoin mining equipment.

- Polynomial Commitments serve as the mathematical foundation necessitating high-throughput modular arithmetic.

- Multi-Scalar Multiplication operations dominate the proof generation cycle, driving the requirement for massive parallelization.

- Hardware Acceleration paths emerged to minimize the time-to-proof, shifting the burden from software-only overhead to silicon-level efficiency.

This transition mirrors the evolution of high-frequency trading infrastructure, where the objective remains the reduction of execution time to the lowest possible threshold. The shift from software-based proof generation to dedicated hardware signals the maturation of decentralized financial systems into professional-grade trading environments.

Theory

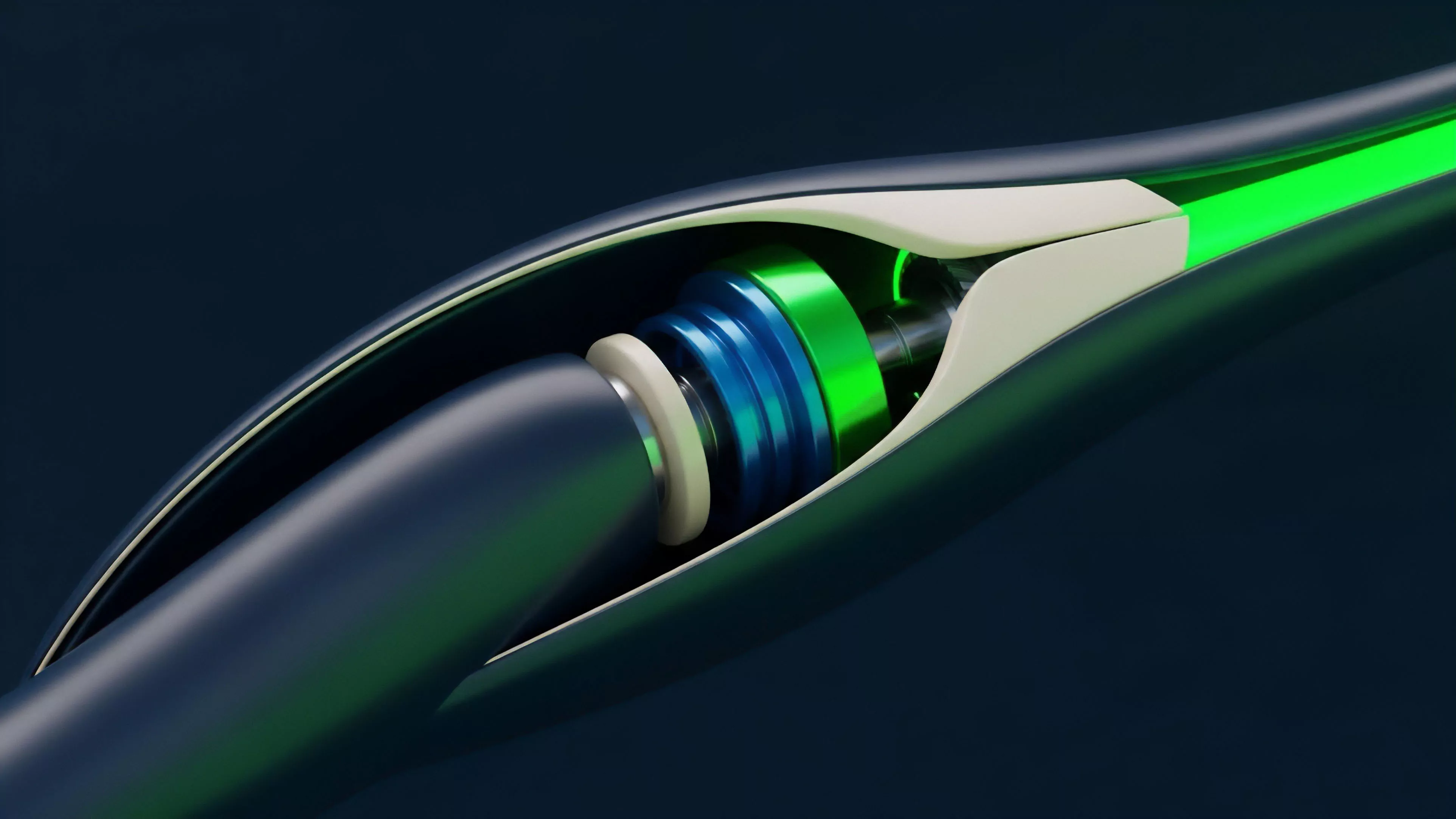

The mechanics of Zero-Knowledge Hardware rely on the efficient parallelization of elliptic curve cryptography. These systems map complex cryptographic functions onto hardware-level logic gates, allowing for simultaneous execution of thousands of independent operations.

| Metric | General Purpose CPU | Dedicated ZK Hardware |

| Throughput | Low | Very High |

| Energy Efficiency | Poor | Optimal |

| Latency | Variable | Deterministic |

The efficiency gains are rooted in the reduction of memory access cycles. By keeping intermediate cryptographic states within high-bandwidth on-chip memory, Zero-Knowledge Hardware bypasses the performance degradation caused by bus contention in standard server architectures.

Deterministic latency in proof generation provides the predictable execution timing necessary for sophisticated derivative pricing and margin management.

This deterministic performance profile is critical for maintaining market microstructure integrity. In an environment where every millisecond influences arbitrage opportunities and liquidation triggers, the ability to generate proofs at a constant, high-speed rate ensures that the system remains responsive under extreme volatility.

Approach

Current implementation strategies focus on the development of hybrid hardware-software stacks. Developers utilize hardware description languages to define the logic for modular arithmetic circuits, which are then deployed onto high-performance silicon.

This approach allows for rapid iteration of cryptographic protocols while maintaining the speed advantages of fixed-function hardware.

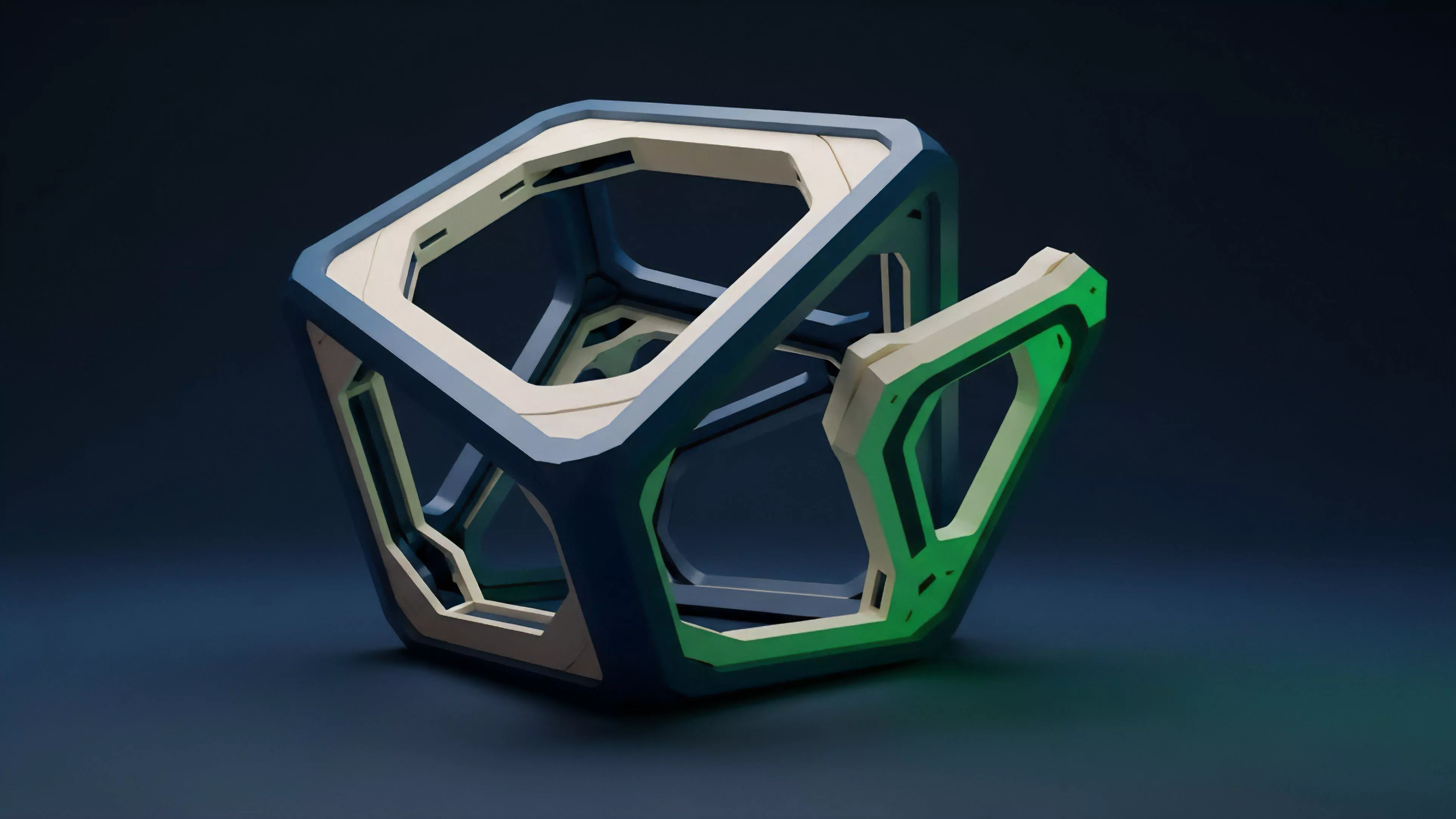

- Field Programmable Gate Arrays provide flexibility for adapting to evolving cryptographic standards.

- Application Specific Integrated Circuits deliver peak efficiency for established, high-volume proof generation tasks.

- Modular Acceleration Units allow protocols to scale capacity incrementally by adding more processing nodes.

The strategic deployment of these units involves placing them at the edge of the network, close to where transaction data originates. This reduces the data transmission overhead, ensuring that the proof generation process does not become a bottleneck for liquidity providers and market makers operating across multiple decentralized venues.

Evolution

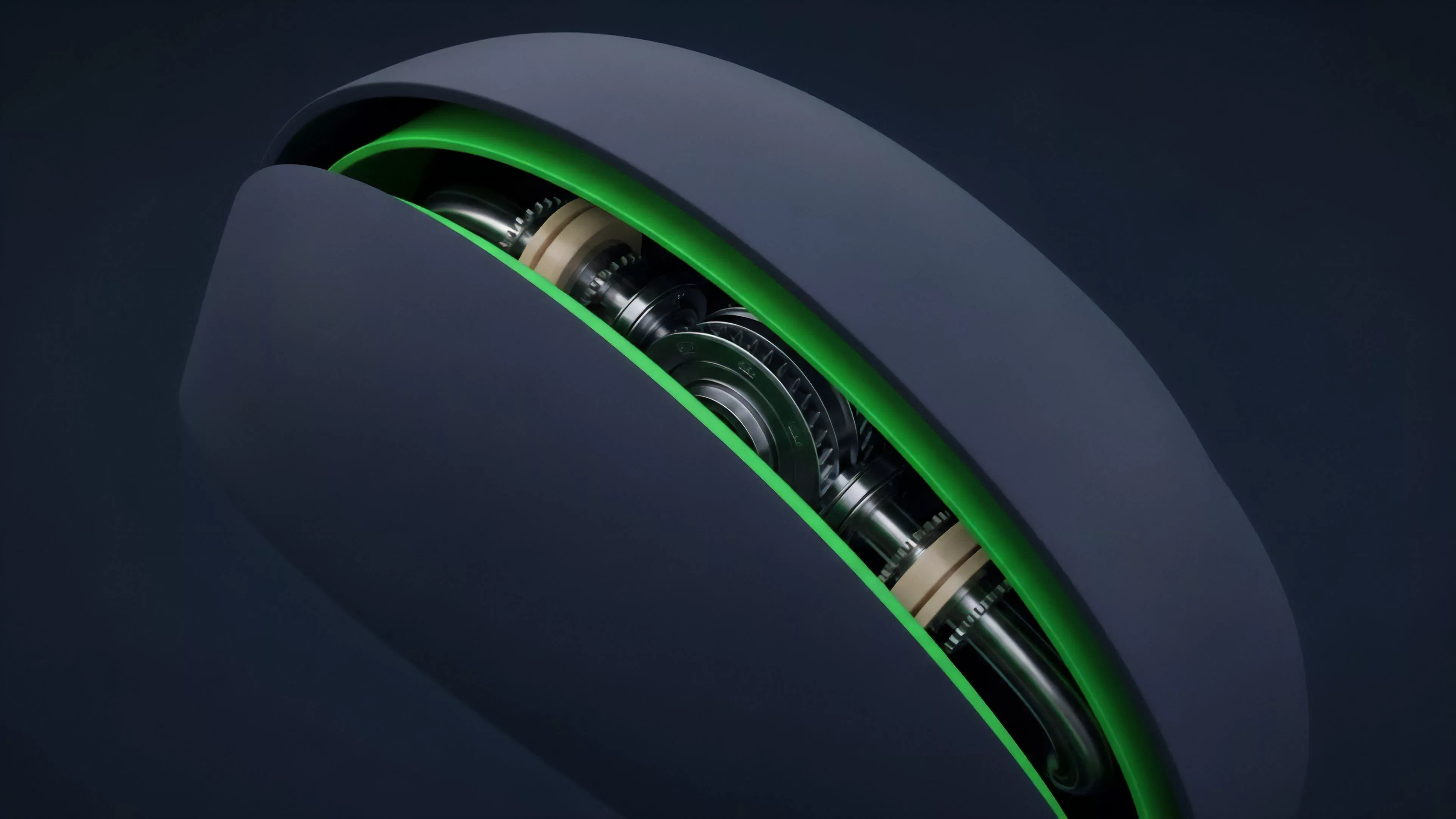

The path from general computation to specialized silicon has been rapid. Early stages involved rudimentary software optimizations, which quickly hit the physical limits of sequential processing.

The current state features the emergence of specialized Zero-Knowledge Hardware firms that provide infrastructure as a service, allowing protocols to rent capacity rather than building proprietary hardware.

Specialized hardware enables decentralized financial protocols to achieve the computational throughput required for high-frequency trading applications.

This evolution tracks the history of financial technology, where infrastructure shifts from commodity hardware to purpose-built execution engines. The current focus centers on lowering the barrier to entry for proof generation, moving from high-cost, proprietary designs to standardized hardware modules that integrate into existing cloud and edge infrastructure. The industry is currently witnessing a transition where the hardware itself is becoming a commoditized, yet essential, component of the financial layer.

Horizon

The future of Zero-Knowledge Hardware involves the integration of these modules directly into consumer-grade devices and edge-computing nodes.

This decentralization of the hardware layer ensures that proof generation is not concentrated in the hands of a few large operators, mitigating systemic risk and enhancing the resilience of the overall financial network.

| Phase | Primary Objective |

| Current | Performance Scaling |

| Near-Term | Standardization |

| Long-Term | Ubiquitous Integration |

As these systems become more efficient, the cost of private transaction settlement will decline, enabling the widespread adoption of complex derivative instruments that were previously impractical. The ultimate realization is a financial system where privacy and performance are native features of the underlying hardware, rather than an additional layer of complexity. What fundamental limit will we reach when the speed of cryptographic proof generation surpasses the speed of the underlying network propagation?