Capital Optimization

Meaning ⎊ Capital optimization in crypto options focuses on minimizing collateral requirements through advanced portfolio risk modeling to enhance capital efficiency and systemic integrity.

Prover Verifier Model

Meaning ⎊ The Prover Verifier Model uses cryptographic proofs to verify financial transactions and collateral without revealing private data, enabling privacy preserving derivatives.

Transaction Cost Optimization

Meaning ⎊ Strategies to minimize trading expenses including exchange fees and gas costs to enhance net portfolio performance and returns.

Order Book Design and Optimization Techniques

Meaning ⎊ Order Book Design and Optimization Techniques are the architectural and algorithmic frameworks governing price discovery and liquidity aggregation for crypto options, balancing latency, fairness, and capital efficiency.

Order Book Design and Optimization Principles

Meaning ⎊ Order Book Design and Optimization Principles govern the deterministic matching of financial intent to maximize capital efficiency and price discovery.

Order Book Design Principles and Optimization

Meaning ⎊ The core function of options order book design is to create a capital-efficient, low-latency mechanism for price discovery while managing the systemic risk inherent in non-linear derivative instruments.

Data Feed Cost Optimization

Meaning ⎊ Data Feed Cost Optimization minimizes the economic and technical overhead of synchronizing high-fidelity market data within decentralized protocols.

Hybrid DeFi Model Optimization

Meaning ⎊ The Adaptive Volatility Oracle Framework optimizes crypto options by blending high-speed off-chain volatility computation with verifiable on-chain risk settlement.

Margin Calculation Optimization

Meaning ⎊ Dynamic Risk-Based Portfolio Margin optimizes capital allocation by calculating net portfolio risk across multiple assets and derivatives against a spectrum of adverse market scenarios.

Gas Fee Optimization Strategies

Meaning ⎊ Gas Fee Optimization Strategies are architectural designs minimizing the computational overhead of options contracts to ensure the financial viability of continuous hedging and settlement on decentralized ledgers.

Smart Contract Gas Optimization

Meaning ⎊ Smart Contract Gas Optimization dictates the economic viability of decentralized derivatives by minimizing computational friction within settlement layers.

Order Book Order Type Optimization Strategies

Meaning ⎊ Order Book Order Type Optimization Strategies involve the algorithmic calibration of execution instructions to maximize fill rates and minimize costs.

Order Book Order Matching Algorithm Optimization

Meaning ⎊ Order Book Order Matching Algorithm Optimization facilitates the deterministic and efficient intersection of trade intents within high-velocity markets.

Order Book Order Type Optimization

Meaning ⎊ Order Book Order Type Optimization establishes the technical framework for maximizing capital efficiency and minimizing execution slippage in markets.

Zero Knowledge Rollup Prover Cost

Meaning ⎊ The Zero Knowledge Rollup Prover Cost defines the computational and economic threshold for generating validity proofs to ensure trustless scalability.

Calldata Cost Optimization

Meaning ⎊ Calldata Cost Optimization is the fundamental engineering discipline that minimizes the data storage overhead for options protocols, directly enabling capital efficiency and market depth.

Gas Cost Optimization Strategies

Meaning ⎊ Gas Cost Optimization Strategies involve the technical and architectural reduction of computational overhead to ensure protocol viability.

Order Book Structure Optimization Techniques

Meaning ⎊ Dynamic Volatility-Weighted Order Tiers is a crypto options optimization technique that structurally links order book depth and spacing to real-time volatility metrics to enhance capital efficiency and systemic resilience.

Order Book Structure Optimization

Meaning ⎊ Order Book Structure Optimization creates a Hybrid Liquidity Architecture, synthesizing CLOB and AMM mechanics to ensure dynamic, capital-efficient pricing and deep liquidity for non-linear crypto options.

Transaction Processing Optimization

Meaning ⎊ Decentralized Atomic Settlement Layer (DASL) is a two-layer protocol that uses cryptographic proofs to achieve near-instantaneous, low-cost options transaction finality, significantly boosting capital efficiency and mitigating systemic liquidation risk.

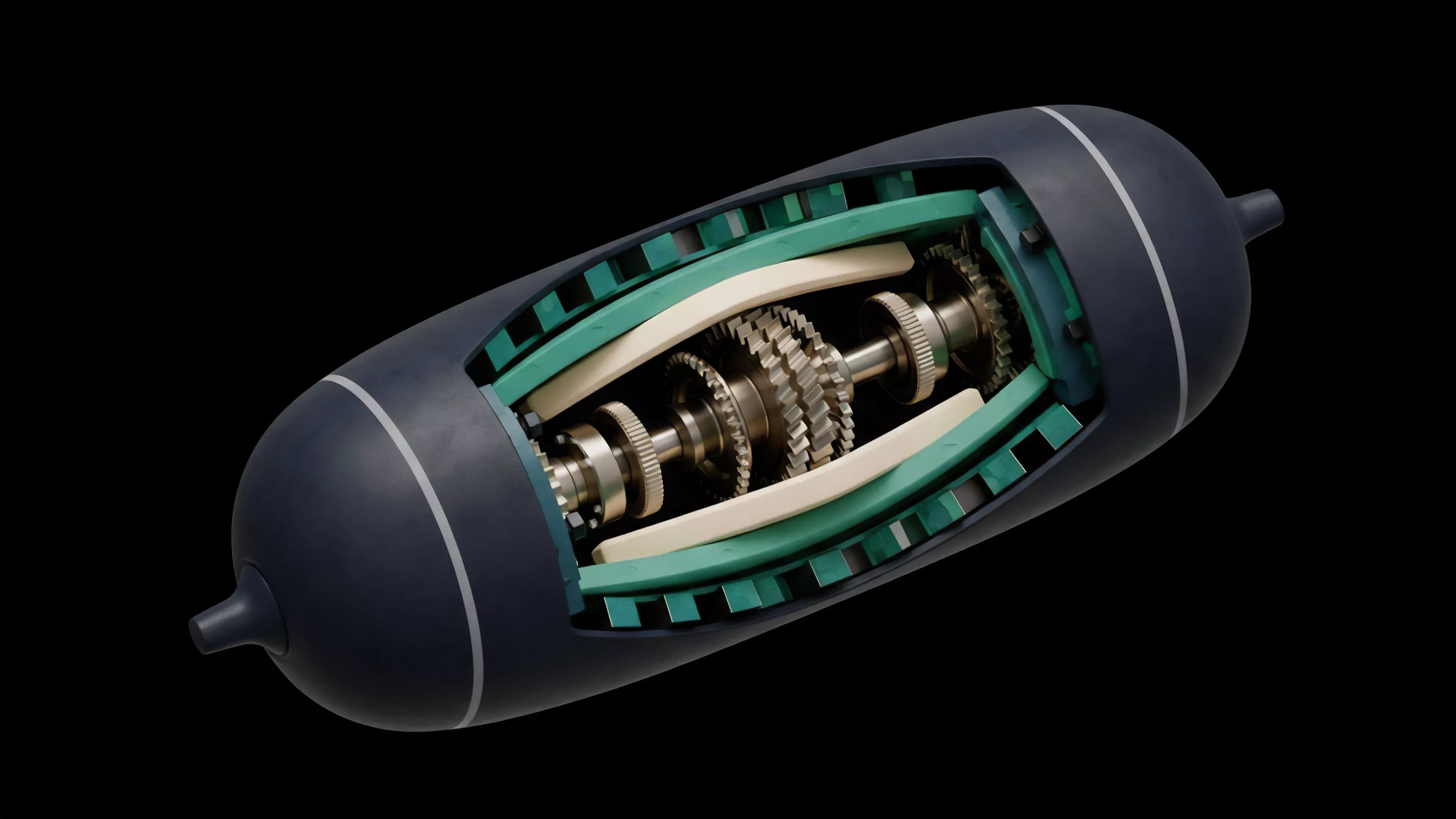

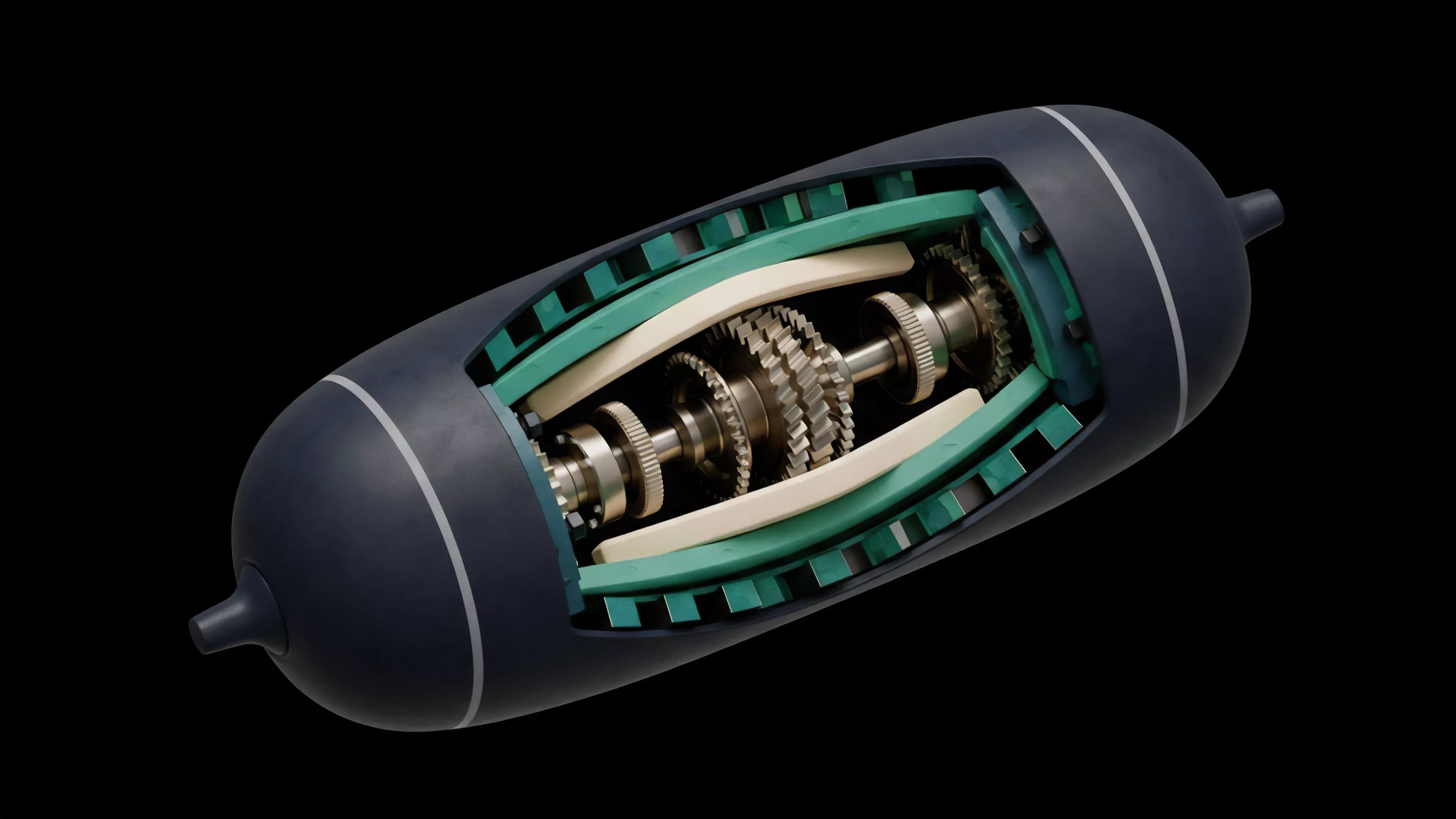

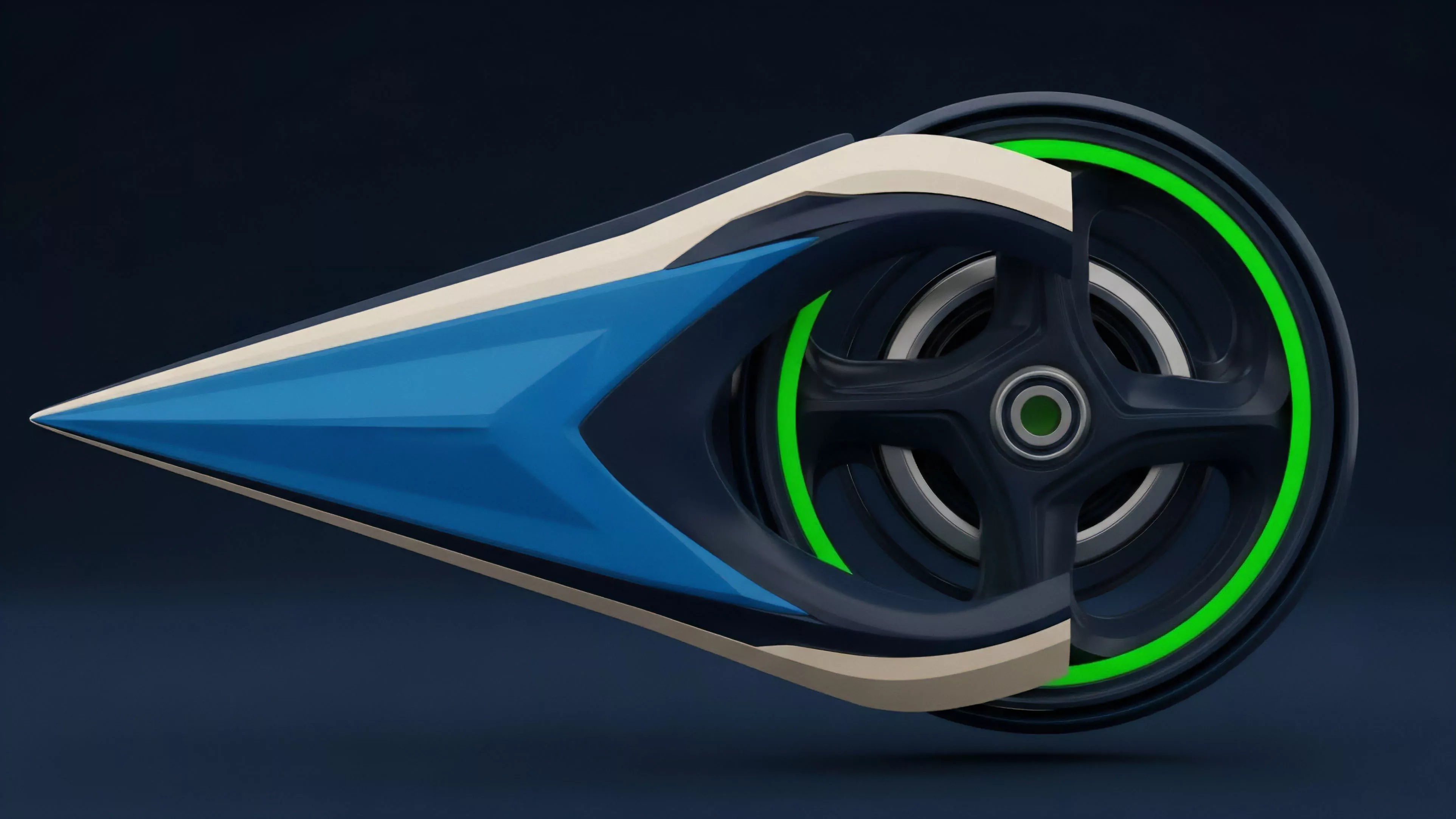

Hardware Acceleration

Meaning ⎊ Using specialized hardware like FPGAs to perform complex calculations at speeds faster than standard software.

Prover Efficiency

Meaning ⎊ Prover Efficiency determines the operational ceiling for high-frequency decentralized derivatives by linking computational latency to settlement finality.

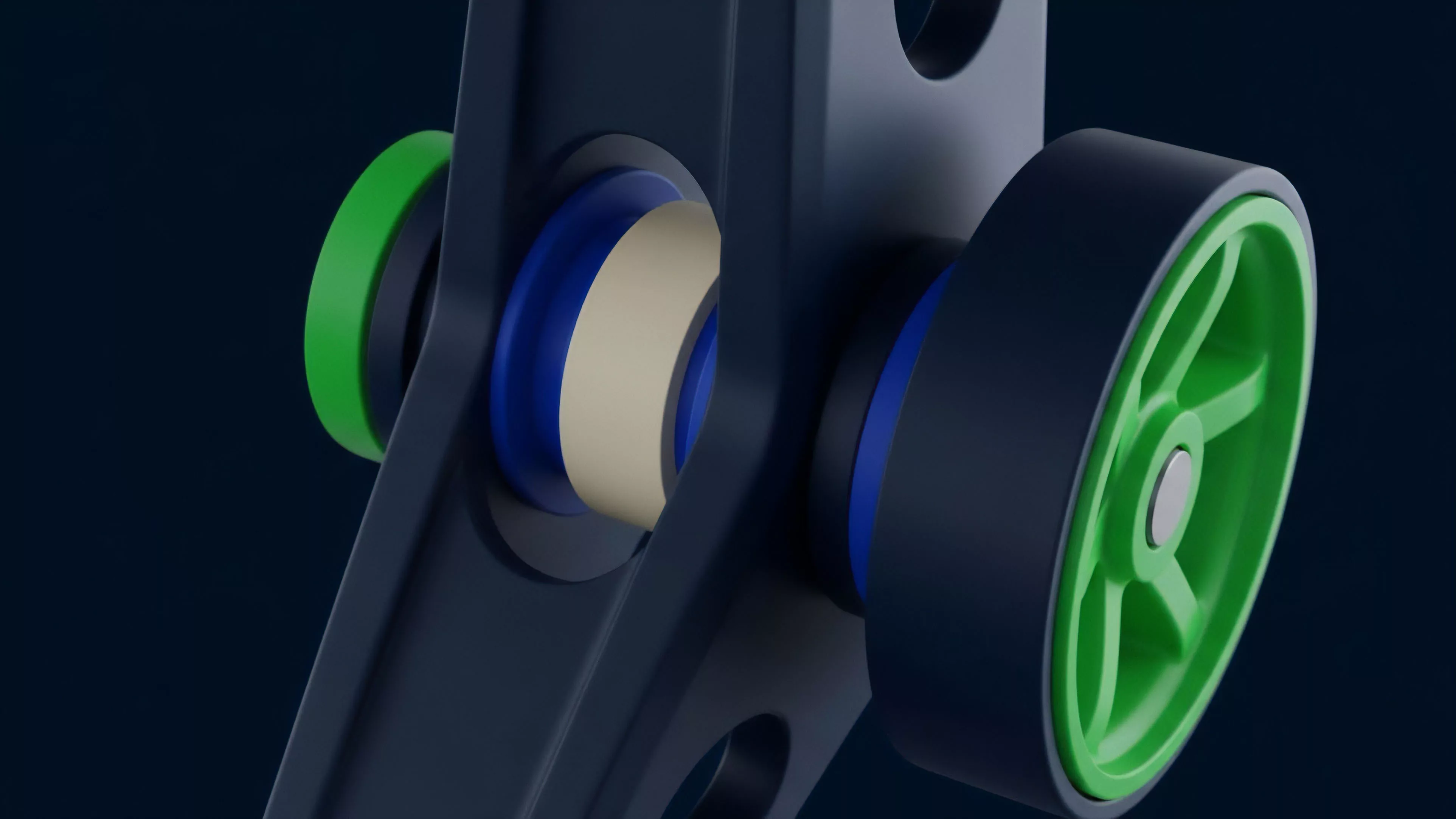

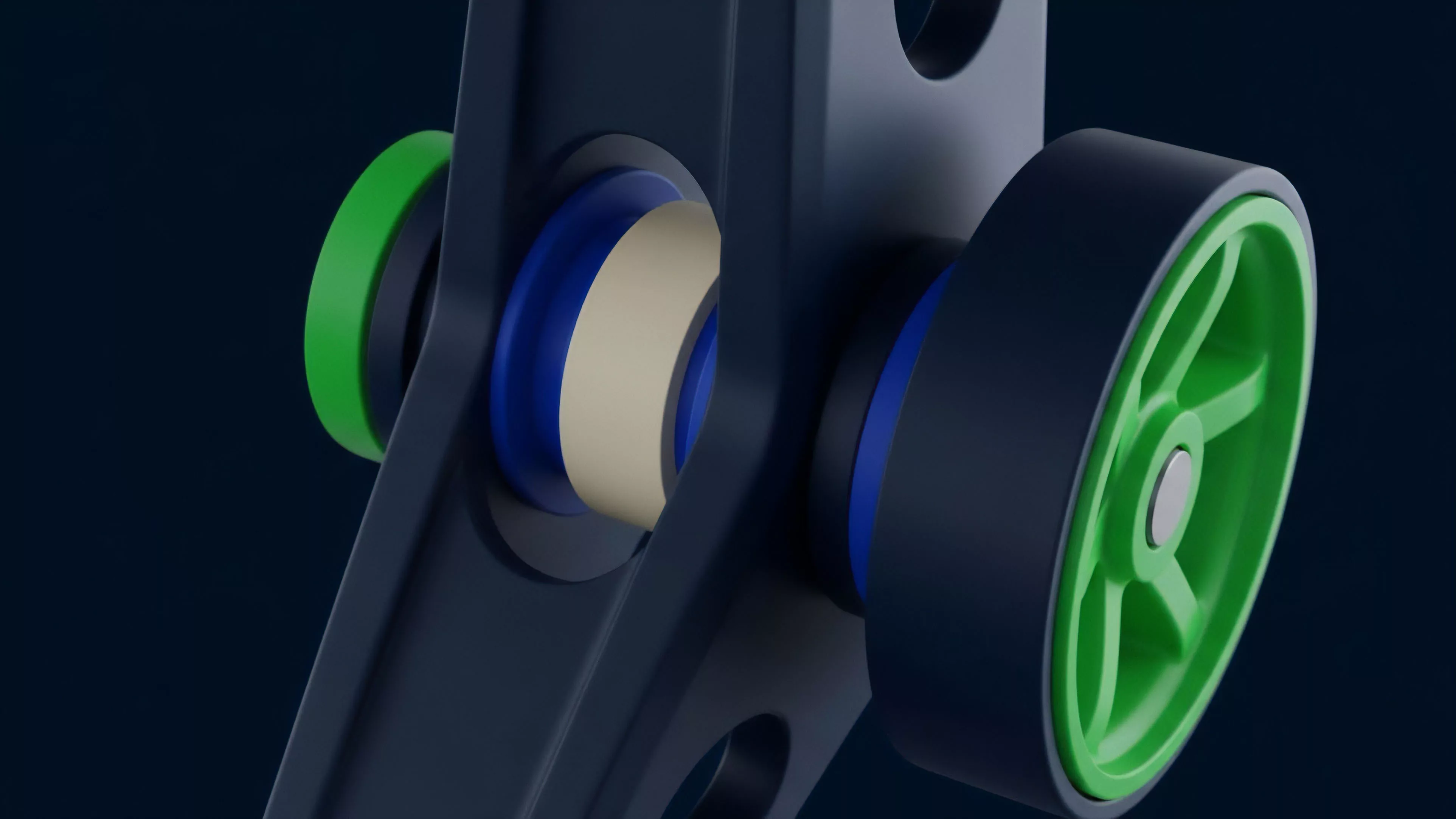

Hardware Security Modules

Meaning ⎊ Tamper-resistant physical devices used for secure cryptographic key management and transaction signing.

Hardware-Agnostic Proof Systems

Meaning ⎊ Hardware-Agnostic Proof Systems replace physical silicon trust with mathematical verification to secure decentralized financial settlement layers.

Multi Prover Model

Meaning ⎊ Multi Prover Model establishes cryptographic redundancy by requiring consensus across independent proof systems to eliminate single points of failure.

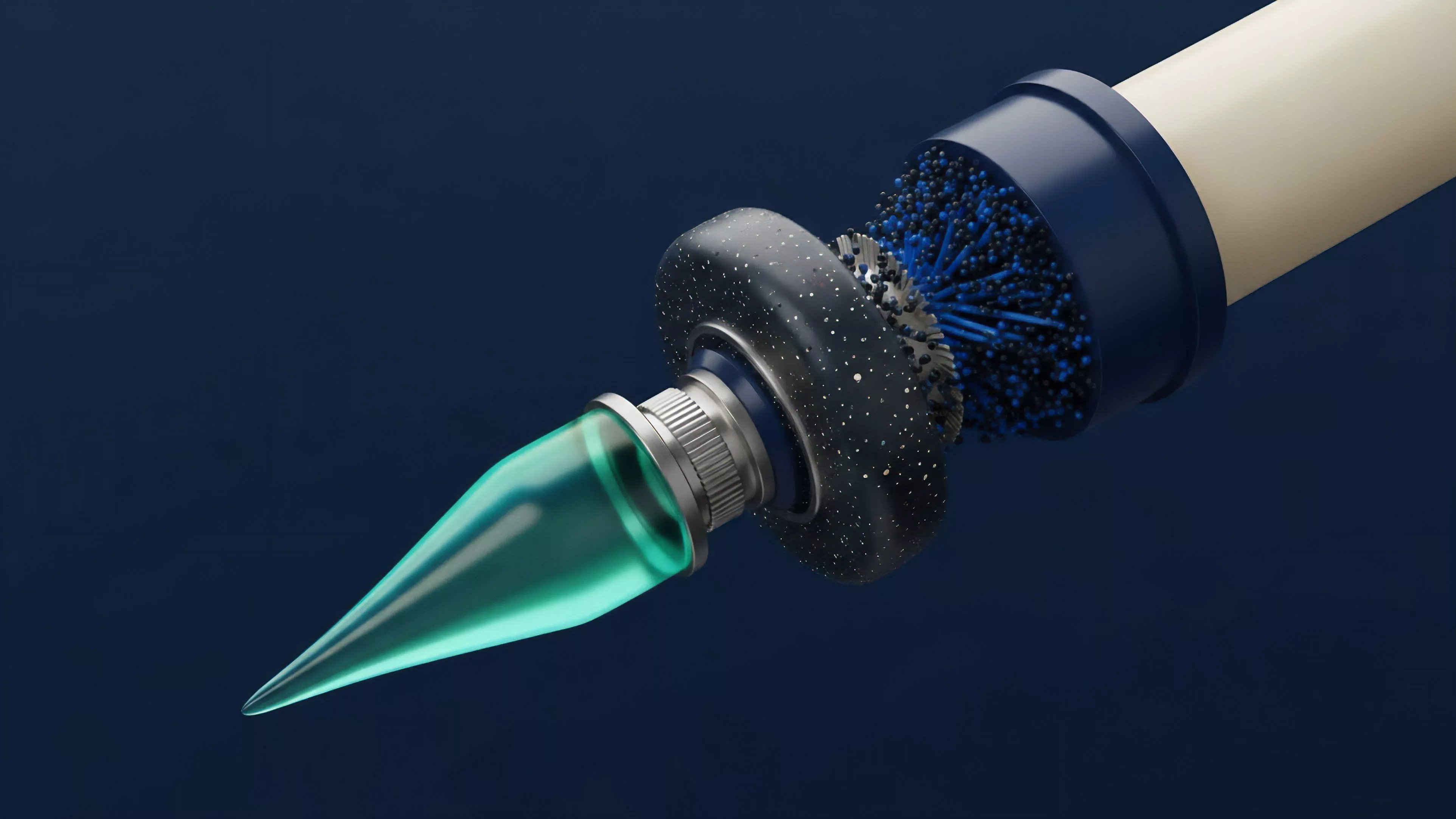

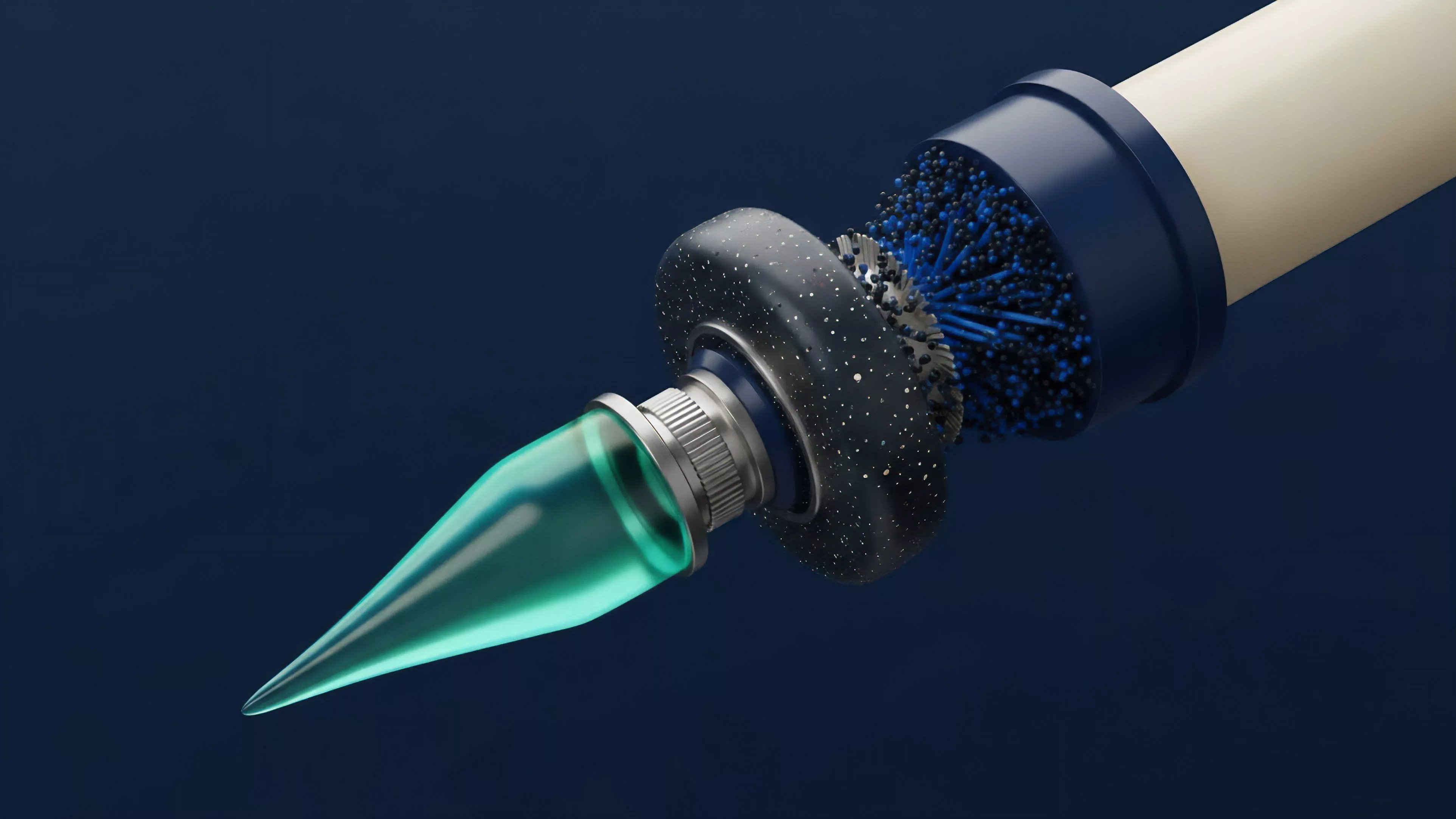

Zero Knowledge Prover

Meaning ⎊ Zero Knowledge Prover facilitates private, verifiable derivative settlement by enabling computational integrity without exposing sensitive data.

Hardware Depreciation

Meaning ⎊ The process of allocating the cost of node hardware over its useful life to reflect its decreasing value and utility.

Zero-Knowledge Hardware

Meaning ⎊ Zero-Knowledge Hardware provides the essential computational throughput required to enable scalable, private, and high-frequency decentralized finance.

Prover Computational Overhead

Meaning ⎊ The intensive computational resources required to generate cryptographic proofs, creating potential barriers to entry.