Hardware-Agnostic Proof Systems

Meaning ⎊ Hardware-Agnostic Proof Systems replace physical silicon trust with mathematical verification to secure decentralized financial settlement layers.

Hardware Security Modules

Meaning ⎊ Physical, tamper-resistant devices designed to store and manage cryptographic keys securely within isolated environments.

Public Blockchain Matching Engines

Meaning ⎊ Public Blockchain Matching Engines provide a transparent, deterministic framework for global liquidity coordination, replacing trust with verifiable code.

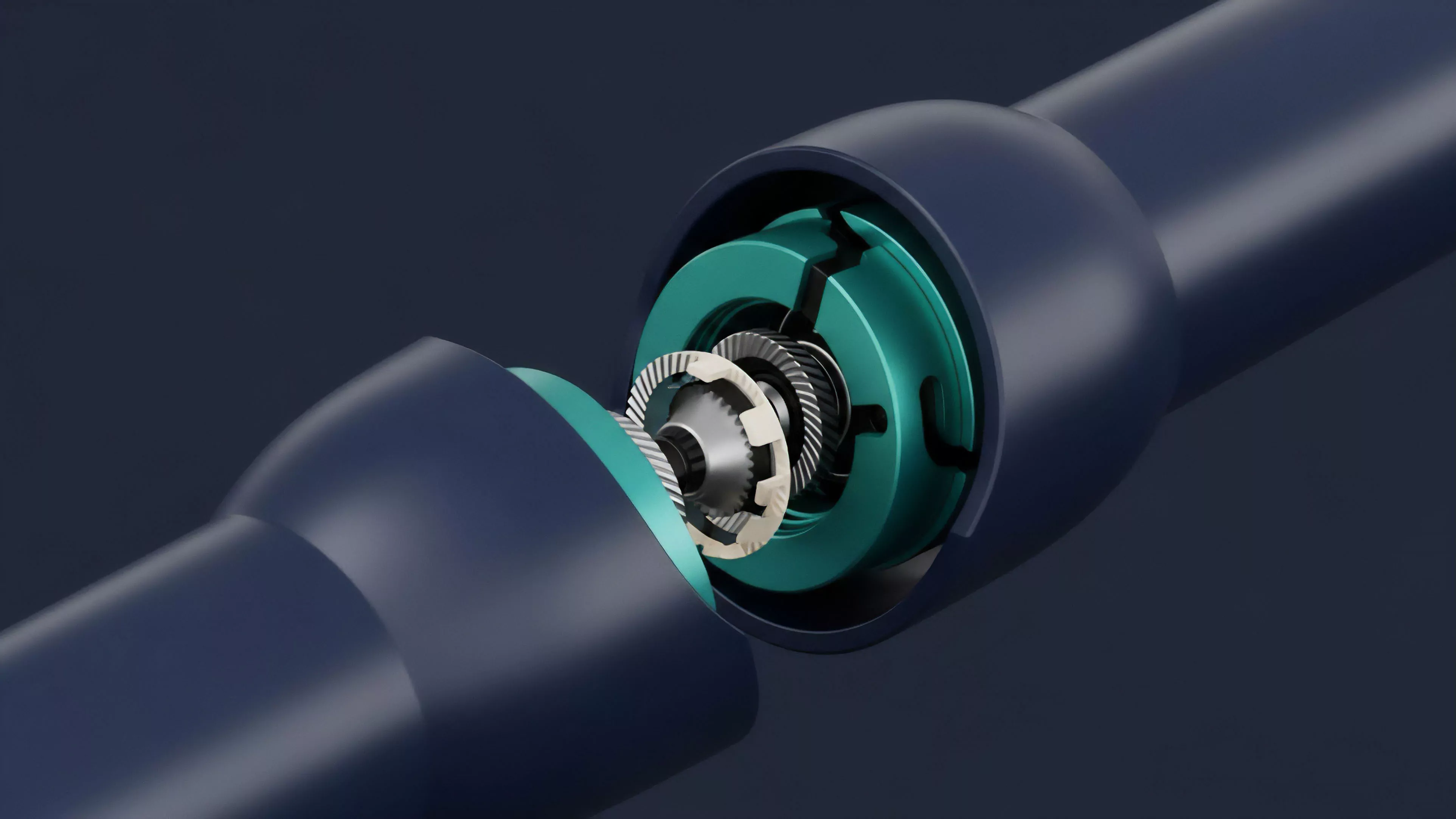

Hardware Acceleration

Meaning ⎊ Utilizing specialized hardware to perform high-speed computations and reduce latency in financial transactions.

Order Book Matching Engines

Meaning ⎊ The Order Book Matching Engine is the high-speed, adversarial core of a crypto options exchange, determining price discovery, capital efficiency, and the systemic risk management capacity for complex derivative exposures.

Dynamic Margin Engines

Meaning ⎊ The Dynamic Margin Engine calculates collateral requirements based on a continuous, portfolio-level assessment of potential loss across defined stress scenarios.

Private Margin Engines

Meaning ⎊ Private Margin Engines provide sovereign, privacy-preserving risk computation to isolate counterparty exposure and enhance institutional capital efficiency.

Cross-Chain Margin Engines

Meaning ⎊ Cross-Chain Margin Engines enable unified capital efficiency by synchronizing collateral value and liquidation risk across disparate blockchain networks.

Real-Time Margin Engines

Meaning ⎊ The Real-Time Margin Engine is the computational system that assesses a multi-asset portfolio's net risk exposure to dynamically determine capital requirements and enforce liquidations.

Automated Compliance Engines

Meaning ⎊ Software systems that monitor and enforce regulatory compliance through real-time automated data analysis.

AI Risk Engines

Meaning ⎊ AI Risk Engines dynamically manage systemic risk in crypto options by replacing static pricing models with predictive machine learning architectures.

Off-Chain Order Matching Engines

Meaning ⎊ Off-chain order matching engines enable high-frequency options trading by separating price discovery from on-chain settlement to achieve CEX-level performance and capital efficiency.

Smart Contract Risk Engines

Meaning ⎊ Smart Contract Risk Engines autonomously govern decentralized derivatives protocols by managing collateral and liquidations to ensure systemic solvency.

High-Throughput Matching Engines

Meaning ⎊ High-throughput matching engines are essential for crypto options, enabling high-speed order execution and complex risk calculations necessary for efficient, liquid derivatives markets.

Predictive Risk Engines

Meaning ⎊ A Predictive Risk Engine forecasts and dynamically manages the systemic and liquidation risks inherent in decentralized crypto derivatives by modeling non-linear volatility and collateral requirements.

Order Matching Engines

Meaning ⎊ The central software system within an exchange that matches buy and sell orders to facilitate trades.

Decentralized Risk Engines

Meaning ⎊ Decentralized risk engines autonomously manage collateral and liquidation parameters for derivatives protocols, mitigating systemic risk through transparent, on-chain mechanisms.

Real-Time Risk Engines

Meaning ⎊ Real-Time Risk Engines provide continuous, automated solvency calculations for crypto derivatives protocols by analyzing portfolio sensitivities and enforcing margin requirements.

Autonomous Risk Engines

Meaning ⎊ Autonomous Risk Engines are automated systems that calculate and adjust risk parameters for decentralized derivatives protocols, ensuring solvency and optimizing capital efficiency in volatile markets.

Off-Chain Matching Engines

Meaning ⎊ Systems that match orders outside the blockchain to provide high-speed trading performance.

Off-Chain Risk Engines

Meaning ⎊ External systems that perform high-speed risk modeling and position monitoring for decentralized derivative protocols.

Automated Liquidation Engines

Meaning ⎊ Protocol mechanisms that automatically execute collateral sales to maintain solvency during market volatility.

On Chain Risk Engines

Meaning ⎊ On Chain Risk Engines autonomously calculate and enforce dynamic risk parameters within decentralized protocols to ensure solvency and optimize capital efficiency for derivatives and lending positions.

Automated Risk Engines

Meaning ⎊ Software systems that monitor risk parameters and trigger automated protective actions to maintain protocol solvency in real-time.

Risk Engines

Meaning ⎊ Computational systems that monitor portfolio risk, calculate margin, and manage liquidations in real time.

Liquidation Engines

Meaning ⎊ Automated systems that manage the rapid closure of under-collateralized positions to maintain exchange solvency.

Margin Engines

Meaning ⎊ Protocol components that monitor collateral health, enforce margin requirements, and trigger liquidations.