Essence

Zero Knowledge Proof Acceleration defines the specialized hardware and algorithmic optimization techniques engineered to reduce the computational latency inherent in generating cryptographic proofs. In decentralized finance, the bottleneck for high-frequency trading and complex derivative settlement often lies in the intense processing power required for recursive SNARK or STARK generation. Zero Knowledge Proof Acceleration addresses this by shifting the burden from general-purpose CPUs to purpose-built silicon architectures like FPGAs, ASICs, and highly parallelized GPU kernels.

Zero Knowledge Proof Acceleration provides the computational throughput necessary for real-time cryptographic verification in decentralized order books.

The systemic relevance of this acceleration centers on capital efficiency. When participants execute complex options strategies or delta-neutral hedging, the speed of proof generation dictates the time-to-settlement for on-chain clearinghouses. By minimizing this duration, Zero Knowledge Proof Acceleration enables the transition from batch-processed financial transactions to continuous, high-fidelity market participation.

Origin

The genesis of this field traces back to the fundamental tension between cryptographic privacy and computational overhead.

Early implementations of ZK-rollups struggled with high gas costs and slow finality times, which hindered their adoption for professional-grade derivatives. The transition from theoretical whitepapers to practical hardware deployment was driven by the realization that software-level optimizations reach a point of diminishing returns.

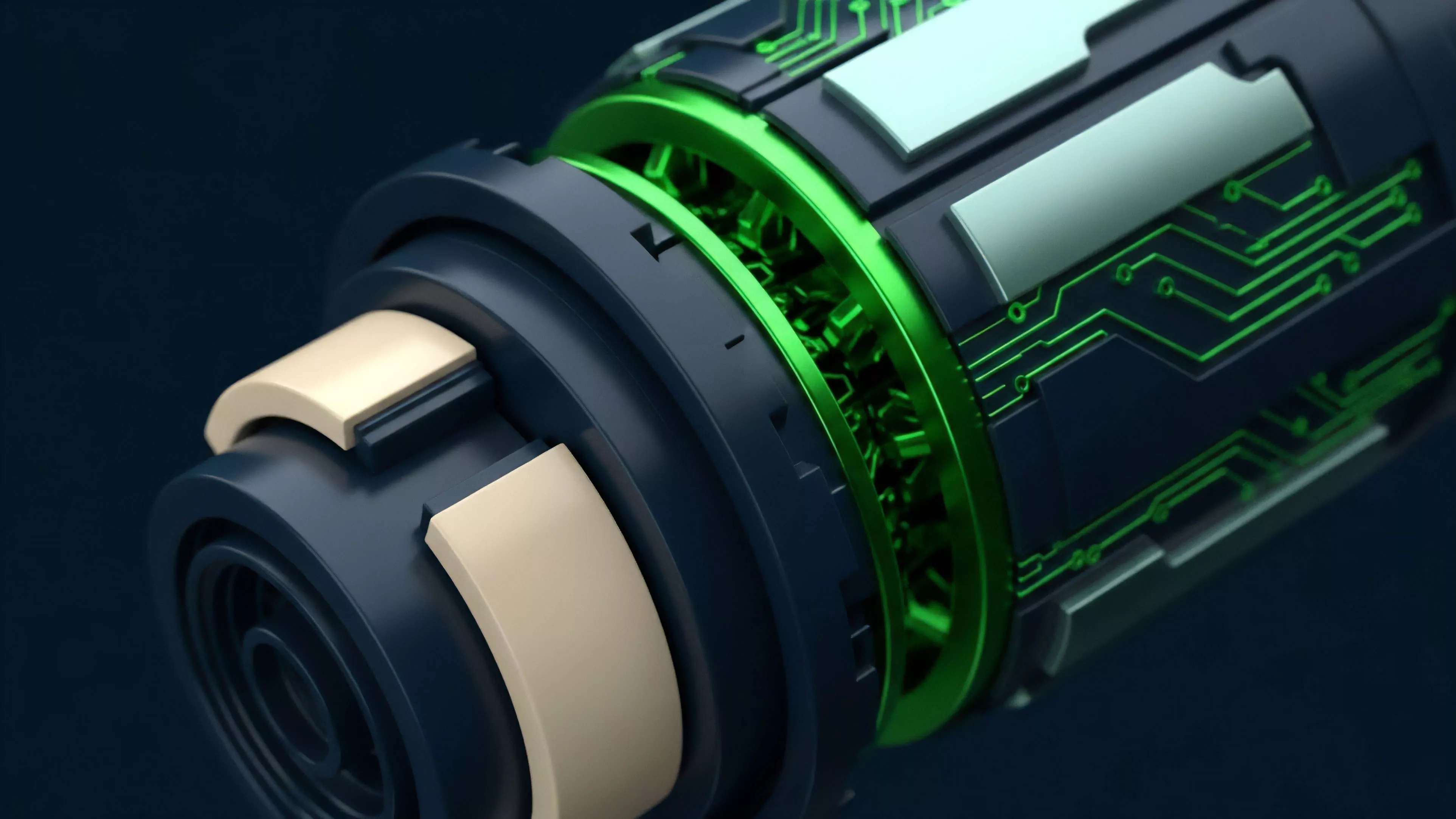

- Hardware Offloading: Initial experiments utilized GPUs to parallelize the Fast Fourier Transforms essential for polynomial commitment schemes.

- Custom Silicon: Developers moved toward FPGA prototyping to exploit the bit-level parallelism required for specific elliptic curve operations.

- Algorithmic Refinement: The evolution of proof systems themselves, shifting toward smaller, more efficient structures, created a feedback loop with hardware design.

This trajectory reflects a classic maturation cycle in computing, where a resource-intensive cryptographic primitive moves from academic abstraction to hardware-accelerated utility. The primary driver was the necessity of maintaining low-latency state transitions in permissionless environments without sacrificing the underlying cryptographic security model.

Theory

The architecture of Zero Knowledge Proof Acceleration relies on the decomposition of proof generation into discrete, parallelizable mathematical tasks. Most modern systems utilize the following components to achieve performance gains:

| Component | Functional Role |

| Multi-Scalar Multiplication | Primary computational driver in SNARK generation |

| Number Theoretic Transform | Core operation for polynomial evaluation and interpolation |

| Memory Interconnects | Bandwidth management for large witness data sets |

The mathematical rigor involves balancing the trade-offs between proof size and verification speed. A significant challenge remains the memory wall; as proofs grow in complexity, the data movement between the processor and storage often exceeds the compute time itself. Efficient acceleration requires a tightly coupled memory architecture that minimizes latency for these specific arithmetic operations.

Effective acceleration strategies prioritize the optimization of multi-scalar multiplication and polynomial commitment operations within specialized silicon.

The adversarial nature of blockchain networks mandates that any acceleration technique must maintain absolute cryptographic soundness. This means the hardware must adhere strictly to the underlying field arithmetic without introducing vulnerabilities that could be exploited to forge proofs. The system operates under the constant pressure of minimizing latency while maximizing the security guarantees of the underlying proof system.

Approach

Current implementations focus on a hybrid stack that bridges high-level cryptographic libraries with low-level hardware primitives.

Development teams typically employ a tiered approach to deployment:

- Software Profiling: Identifying the most time-consuming operations within the prover’s execution flow.

- Kernel Optimization: Rewriting identified bottlenecks into CUDA or OpenCL for massive parallelization on existing GPU infrastructure.

- Hardware Synthesis: Translating verified kernels into hardware description languages for deployment on FPGAs or custom ASIC production.

Market participants currently leverage these accelerated provers to maintain competitive advantages in decentralized liquidity pools. For an automated market maker or a derivatives protocol, the ability to generate proofs in milliseconds rather than seconds directly correlates to higher liquidity and reduced slippage. This efficiency is the foundation for creating complex financial instruments that require rapid, multi-party state updates.

Evolution

The field has moved from experimental GPU clusters to dedicated hardware-as-a-service models.

Early efforts focused on generic compute resources, whereas current developments emphasize extreme specialization. This evolution mirrors the history of Bitcoin mining, yet with a distinct focus on verifiable computation rather than probabilistic hash discovery. The shift toward modular hardware architectures allows protocols to swap proof-generation modules as new, more efficient cryptographic primitives are discovered.

This modularity is a critical survival mechanism in a rapidly changing landscape where the underlying mathematics of ZK-proofs is subject to constant innovation. It seems that the industry is converging on a standard where proof generation becomes a commoditized service, decoupled from the core application logic of the derivative protocol.

Hardware modularity enables protocols to remain resilient against the rapid obsolescence of specific cryptographic proof systems.

Market structures have adjusted accordingly, with liquidity providers increasingly valuing protocols that utilize these accelerated stacks. The barrier to entry has risen, favoring entities that can secure reliable access to high-performance compute resources, thereby concentrating the ability to provide low-latency market services.

Horizon

The future of Zero Knowledge Proof Acceleration lies in the integration of zero-latency proof generation directly into the client-side environment. As mobile and edge devices gain specialized AI and neural processing units, the potential to repurpose this silicon for cryptographic acceleration increases.

This shift would enable fully private, high-speed derivatives trading directly from user-controlled hardware.

| Development Phase | Primary Focus |

| Near-Term | Cloud-based GPU acceleration for institutional provers |

| Mid-Term | Deployment of custom ASICs in decentralized prover networks |

| Long-Term | On-device cryptographic acceleration for end-user privacy |

Systemic risks will evolve as these systems become more efficient. The concentration of prover power could create new forms of censorship or latency-based front-running, requiring new game-theoretic defenses. The ultimate success of this technology depends on the ability to maintain open, decentralized access to the hardware resources that underpin these cryptographic financial systems.