Essence

Hardware Acceleration represents the physical migration of computational logic from general-purpose processors to specialized silicon architectures designed for specific mathematical primitives. In the domain of crypto derivatives, this transition involves the deployment of Field Programmable Gate Arrays and Application-Specific Integrated Circuits to handle the intense arithmetic requirements of zero-knowledge proofs and high-frequency option pricing models. This structural shift bypasses the inherent bottlenecks of the von Neumann architecture by implementing spatial computing where logic gates are wired to perform specific functions in parallel.

Hardware acceleration dictates the boundary between theoretical liquidity and executable market depth.

The presence of Hardware Acceleration in decentralized markets serves as a stabilizer for order flow. By reducing the time required to calculate Option Greeks ⎊ specifically Delta and Gamma ⎊ market participants can update quotes with higher frequency, narrowing spreads and reducing the risk of toxic flow. This technology enables the execution of complex Monte Carlo simulations and Black-Scholes-Merton calculations at a velocity that matches the arrival rate of market data, ensuring that the volatility surface remains accurate even during periods of extreme price action.

Silicon Sovereignty

The adoption of specialized hardware shifts the power dynamics of protocol governance. When a network relies on Hardware Acceleration for consensus or proof generation, the physical infrastructure becomes a participant in the security model. This creates a high barrier to entry that favors participants with the capital to deploy ASIC clusters, yet it provides a deterministic performance level that software-only solutions cannot reach.

The result is a more resilient settlement layer for complex financial instruments.

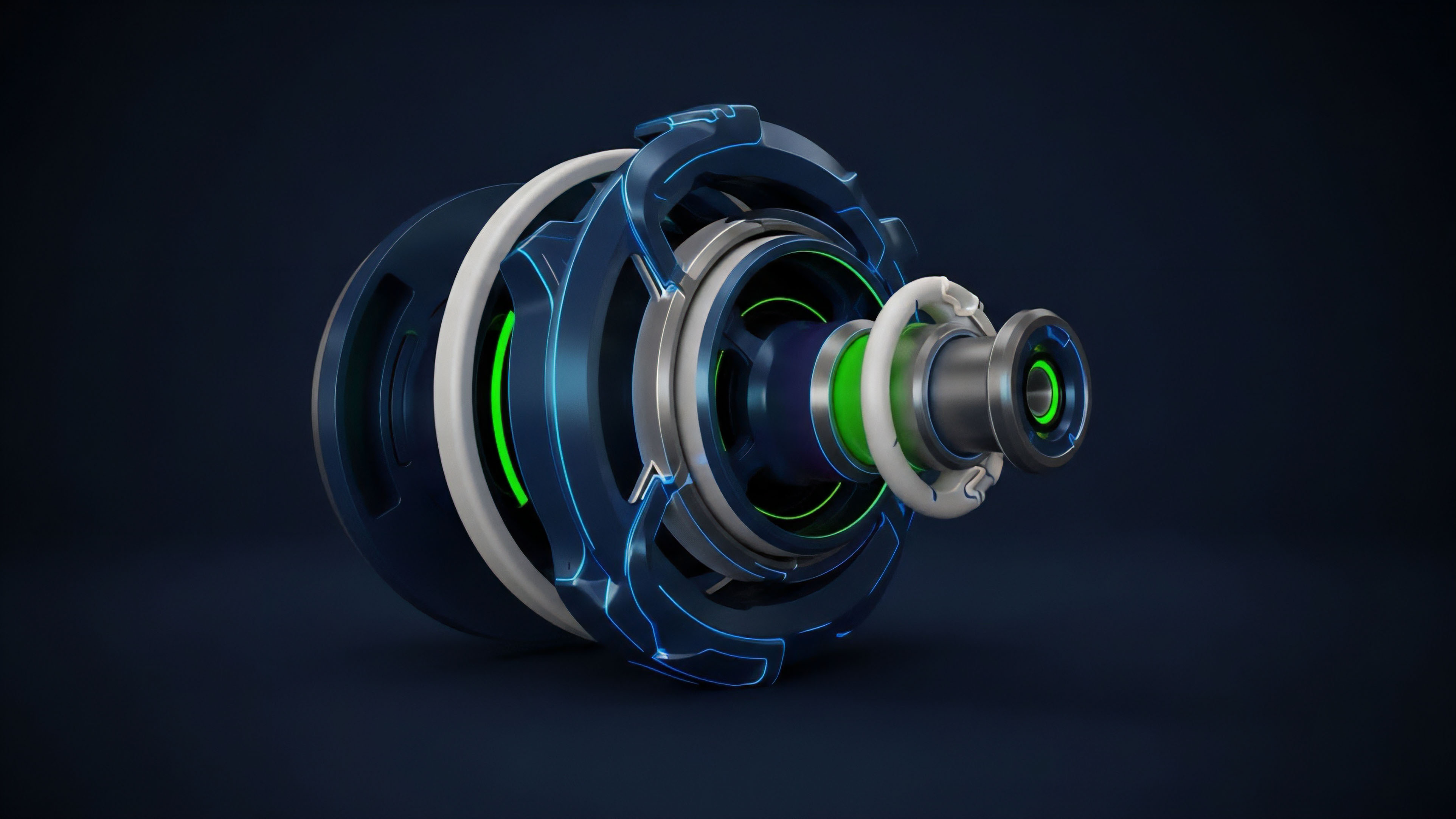

Physical Logic Gates

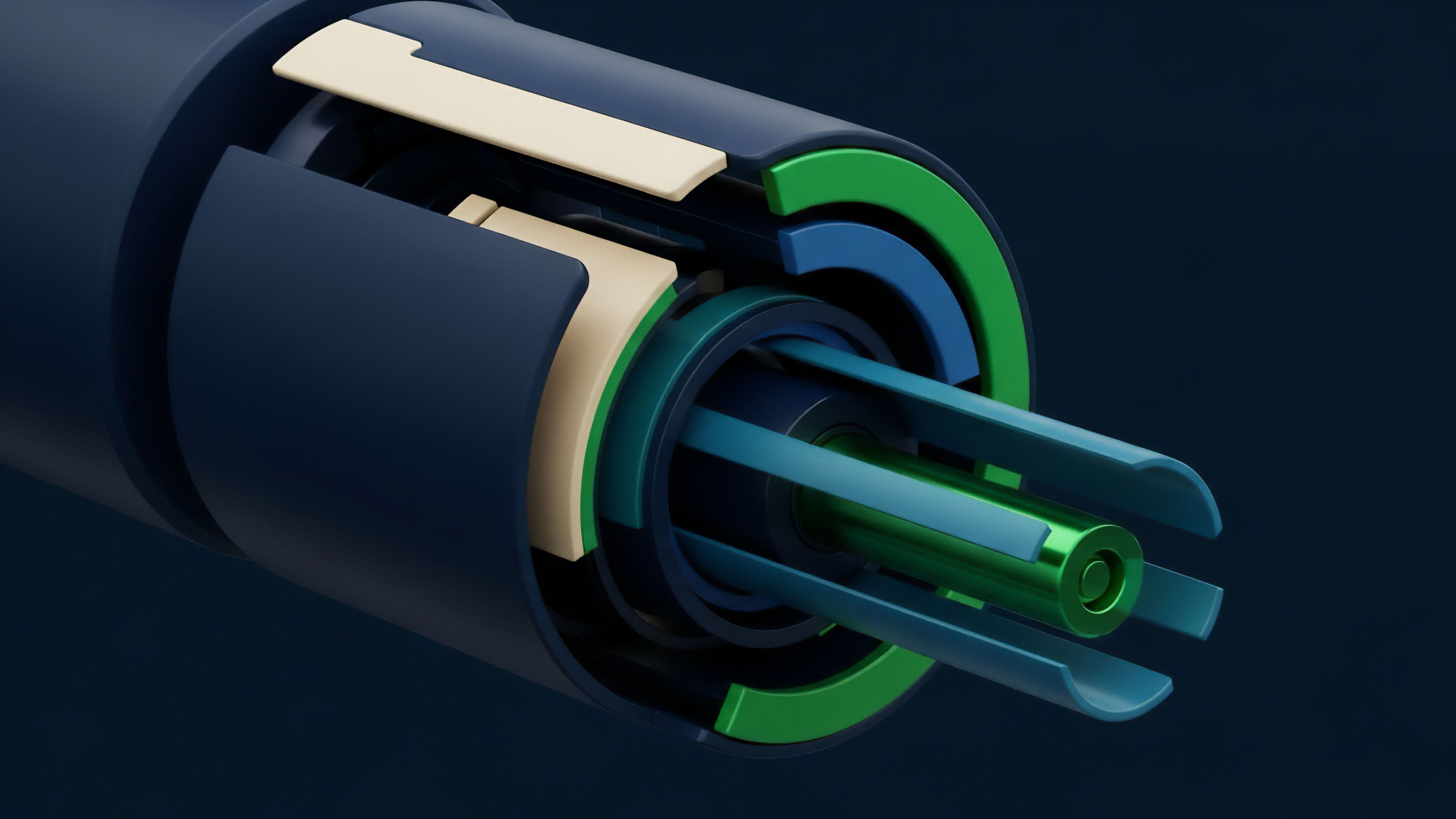

Unlike software that runs on a central processing unit, Hardware Acceleration implements the algorithm directly into the circuitry. This eliminates the overhead of instruction fetching and decoding. For crypto options, this means that the Margin Engine can calculate liquidations for thousands of accounts simultaneously without the latency jitter that plagues traditional cloud-based trading systems.

Origin

The lineage of Hardware Acceleration within the digital asset space began with the transition of Bitcoin mining from CPUs to Graphics Processing Units and eventually to dedicated ASICs.

This progression established the precedent that any computationally expensive cryptographic task will eventually move to specialized silicon. As decentralized finance evolved to include sophisticated derivatives, the need for low-latency execution and high-throughput proof generation became the primary driver for a second wave of hardware specialization.

The transition to specialized silicon marks the end of general-purpose dominance in decentralized finance.

Early decentralized exchanges struggled with the computational cost of maintaining an on-chain Limit Order Book. The latency involved in processing trades on a general-purpose blockchain made it impossible to compete with centralized venues. This friction led to the development of Layer 2 scaling solutions that utilize Zero-Knowledge Rollups.

These rollups require massive amounts of Multi-Scalar Multiplication and Number Theoretic Transforms, operations that are prohibitively slow on standard server hardware but highly efficient when offloaded to FPGAs.

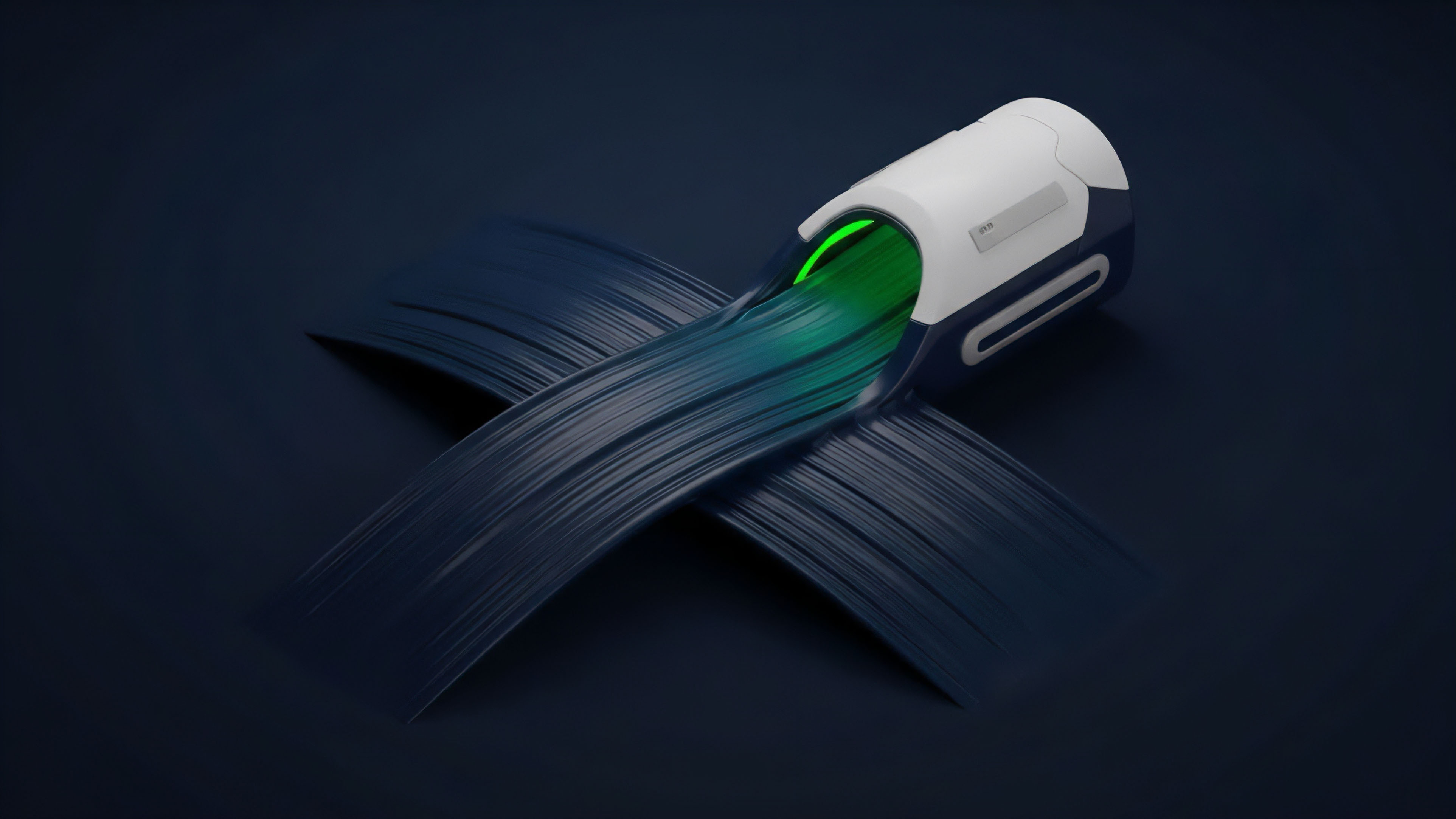

The Latency Floor

The drive for Hardware Acceleration is a response to the “latency floor” of traditional software stacks. Professional market makers in the crypto options space realized that the network stack and the operating system kernel introduced micro-delays that resulted in adverse selection. By moving the entire trading stack ⎊ from packet ingestion to Risk Management ⎊ onto an FPGA, these participants achieved sub-microsecond response times, effectively redefining the competitive landscape of liquidity provision.

Theory

The theoretical basis for Hardware Acceleration rests on the principle of parallel execution and pipelining.

In a standard processor, instructions are processed one after another. In a Hardware Accelerated system, the data flows through a series of dedicated logic blocks that perform different parts of the calculation at the same time. For a Crypto Option, the calculation of Vega and Theta can occur in parallel with the Delta calculation, significantly reducing the total time to reach a risk decision.

| Computation Type | CPU Performance | GPU Performance | FPGA/ASIC Performance |

|---|---|---|---|

| Sequential Logic | High | Low | Medium |

| Parallel Arithmetic | Low | High | Ultra High |

| Latency Jitter | High | Medium | Zero |

| Energy Efficiency | Low | Medium | High |

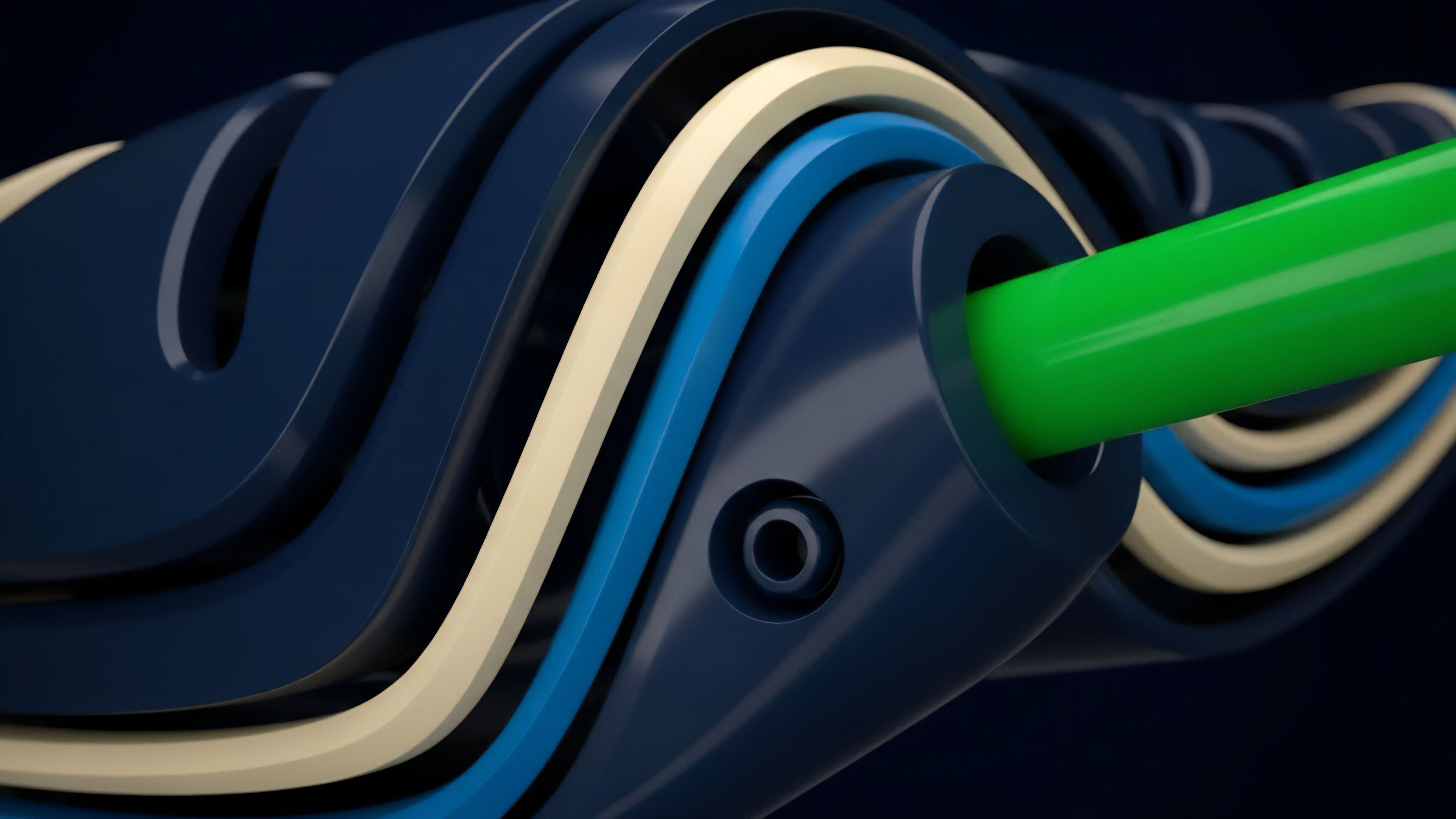

The mathematical complexity of Zero-Knowledge Proofs (ZKPs) provides the most rigorous test for this theory. ZKPs require the computation of large-scale vector-matrix multiplications over finite fields. Hardware Acceleration optimizes these operations by creating custom data paths that match the width of the cryptographic primes being used.

This specialization reduces the energy consumption per proof and increases the number of transactions that a ZK-Rollup can settle per second.

Spatial Vs Temporal Computing

Temporal computing relies on a clock to sequence different operations through a single arithmetic unit. Spatial computing, the foundation of Hardware Acceleration, allocates physical space on the chip for every step of the algorithm. This allows for a continuous stream of data to be processed, which is vital for real-time Volatility Surface fitting.

In an adversarial market, the ability to process data spatially provides a deterministic advantage in price discovery.

Approach

Current implementations of Hardware Acceleration in crypto derivatives focus on the integration of FPGAs into the validator and market maker stacks. FPGAs are preferred over ASICs in this stage because protocol rules and cryptographic primitives are still changing. The reconfigurable nature of FPGAs allows operators to update their hardware logic via software, providing a balance between the speed of silicon and the flexibility of code.

- MSM Acceleration reduces the time required for elliptic curve operations in proof generation.

- NTT Acceleration speeds up the polynomial multiplication used in advanced cryptographic protocols.

- HFT Gateways utilize hardware-level TCP/IP stacks to minimize the time between market signal and order execution.

- Risk Engines implemented in silicon can perform thousands of portfolio stress tests per second to prevent systemic contagion.

Market makers utilize Hardware Acceleration to maintain a Volatility Cube that accounts for different strike prices and expiration dates across multiple assets. By offloading the Greeks calculation to a GPU or FPGA cluster, they can provide continuous liquidity even when the underlying asset experiences high volatility. This approach ensures that the bid-ask spread remains tight, as the market maker has higher confidence in their real-time risk exposure.

Hardware Security Modules

Beyond speed, Hardware Acceleration provides enhanced security through Trusted Execution Environments (TEEs) and Hardware Security Modules (HSMs). These devices accelerate the signing of transactions while keeping private keys isolated from the main operating system. For institutional Crypto Options desks, this hardware-level security is a requirement for managing large-scale collateral and interacting with decentralized clearinghouses.

Evolution

The path of Hardware Acceleration has moved from a niche requirement for Bitcoin miners to a systemic necessity for the entire decentralized financial stack.

Initially, the focus was purely on Hashrate. Today, the focus has shifted to Compute-over-Data and Proof-of-Useful-Work. This evolution reflects the maturing of the market from a simple transfer-of-value system to a complex web of programmable derivatives and synthetic assets.

Future financial stability depends on the verifiable performance of hardware-level risk engines.

The emergence of ZK-ASICs represents the latest stage in this evolution. Companies are now designing chips specifically for the Poseidon Hash and other ZK-friendly algorithms. These chips will likely become as ubiquitous as Bitcoin miners, providing the backbone for a private, scalable financial system.

As these specialized chips become more available, the cost of generating proofs will drop, allowing for more complex On-chain Options that were previously too expensive to execute.

| Era | Dominant Hardware | Primary Financial Use Case |

|---|---|---|

| 2009-2012 | CPU / GPU | Basic Transaction Validation |

| 2013-2017 | ASIC (SHA-256) | Network Security / Mining |

| 2018-2023 | FPGA / GPU Cluster | ZK-Rollups / HFT Market Making |

| 2024-Future | ZK-ASIC / Optical | Hyper-Scalable Derivative Settlement |

The shift toward modularity in blockchain architecture has further accelerated this trend. By separating execution from data availability, protocols can allow specialized hardware providers to handle the heavy lifting of transaction processing. This creates a marketplace for Hardware Acceleration where providers compete on speed and cost, leading to a more efficient allocation of computational resources across the global financial network.

Horizon

The future of Hardware Acceleration lies in the integration of Photonic Computing and Quantum-Resistant Cryptography.

Optical processors, which use light instead of electricity to perform calculations, promise a massive reduction in energy consumption and a significant increase in speed for the linear algebra tasks required in Option Pricing. This will allow for the creation of Hyper-Liquidity pools where millions of quotes are updated in real-time across every possible strike and expiration.

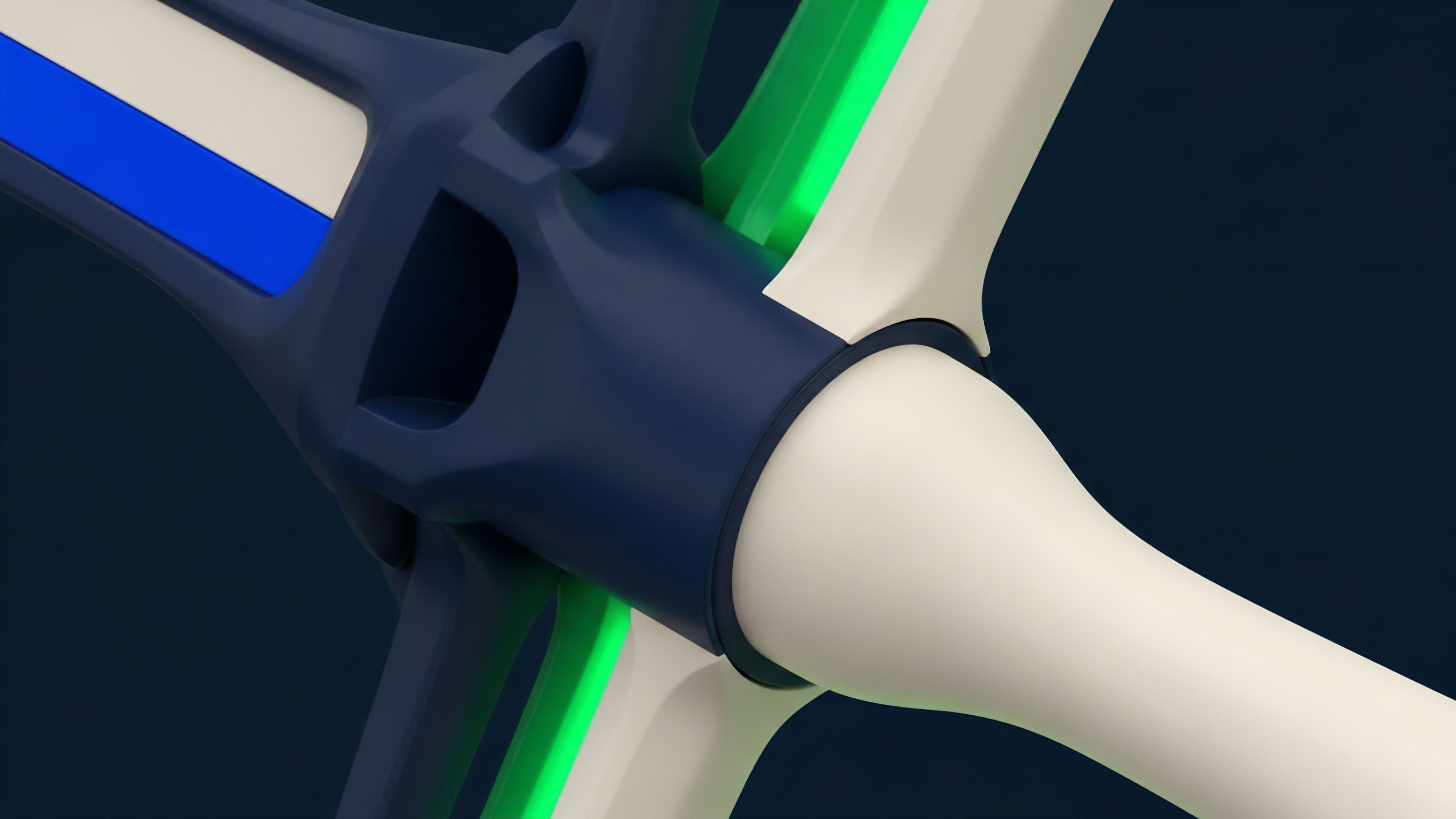

Decentralized Hardware Networks

A shift toward decentralized physical infrastructure networks (DePIN) will allow individuals to contribute Hardware Acceleration power to global derivative protocols. Instead of centralized data centers, a global mesh of FPGAs will provide the proof-generation capacity needed for a truly decentralized global stock exchange. This democratizes access to high-performance computing, allowing smaller protocols to utilize the same level of Risk Acceleration as major financial institutions.

Silicon Risk Management

The ultimate destination for this technology is the implementation of the entire Clearinghouse logic in silicon. By etching the rules of margin, liquidation, and settlement into an ASIC, a protocol can guarantee that these rules are followed without the risk of software bugs or human intervention. This “Hardcoded Finance” will provide a level of certainty and transparency that traditional financial systems cannot match, fostering a new era of trust in decentralized derivative markets.

Glossary

Specialized Silicon

Proof-of-Authority

Cross-Margin

Put Options

Proof Generation

Tee

Risk Engine

Smart Contract Security

Exotic Derivatives