Essence

ASIC Zero Knowledge Acceleration refers to the specialized hardware implementation of cryptographic primitives ⎊ specifically those supporting Zero Knowledge Proofs ⎊ designed to reduce the computational latency inherent in generating proofs for decentralized financial protocols. At its functional core, this hardware replaces general-purpose CPUs or GPUs with circuits hardwired for the modular arithmetic, finite field operations, and elliptic curve pairings that underpin modern cryptographic verification.

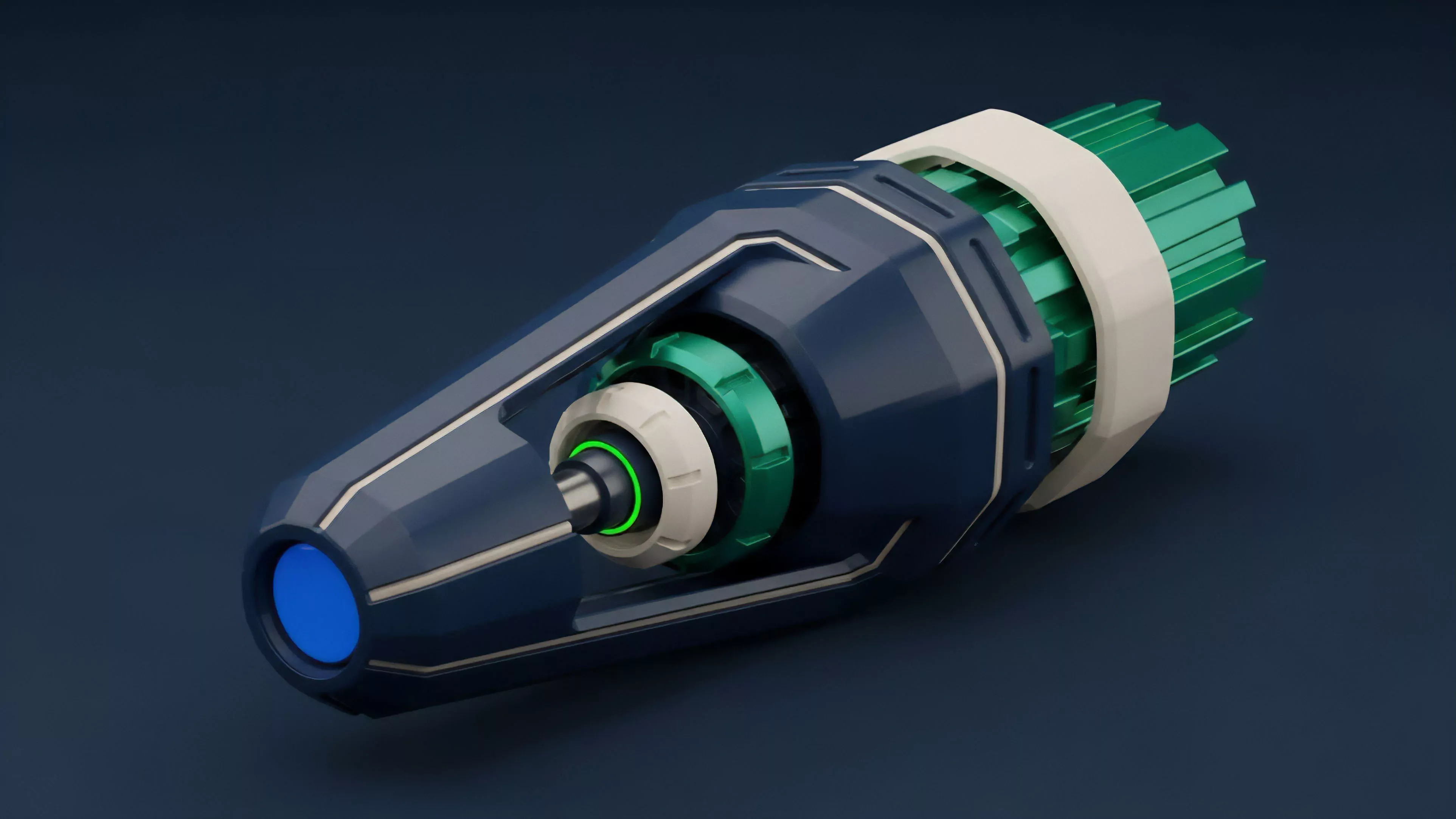

ASIC Zero Knowledge Acceleration functions as the dedicated computational substrate required to enable high-throughput, private financial transaction validation at scale.

The financial significance of this technology lies in its ability to collapse the time-cost barrier for complex transaction validation. By offloading these intensive mathematical tasks to silicon-optimized circuits, protocols achieve higher transaction throughput and lower latency, directly addressing the bottleneck that currently restricts the adoption of privacy-preserving decentralized finance. This transition represents a shift from software-defined verification to hardware-accelerated cryptographic assurance.

Origin

The requirement for ASIC Zero Knowledge Acceleration emerged from the fundamental trade-off between privacy and computational efficiency in blockchain systems. Initial iterations of zero-knowledge implementations, such as early zk-SNARKs, relied on heavy software computation, resulting in proof generation times that rendered real-time financial settlement impractical for high-frequency trading environments.

- Cryptographic Bottlenecks: The intense demand for multi-scalar multiplication and number theoretic transforms necessitated a move away from general-purpose architectures.

- Hardware Specialization: Parallels exist in the evolution of Bitcoin mining, where the transition from CPU to GPU to ASIC provided the necessary efficiency gains for network security.

- Financial Scaling: Market demand for private order books and confidential settlement created the economic incentive to fund the research and development of dedicated silicon.

This path reflects the broader history of financial technology, where the drive for speed and scale consistently pushes computational tasks from flexible software layers into rigid, high-performance hardware structures. The industry moved toward this hardware-centric model as the complexity of proof systems outpaced the linear improvements in traditional processor speeds.

Theory

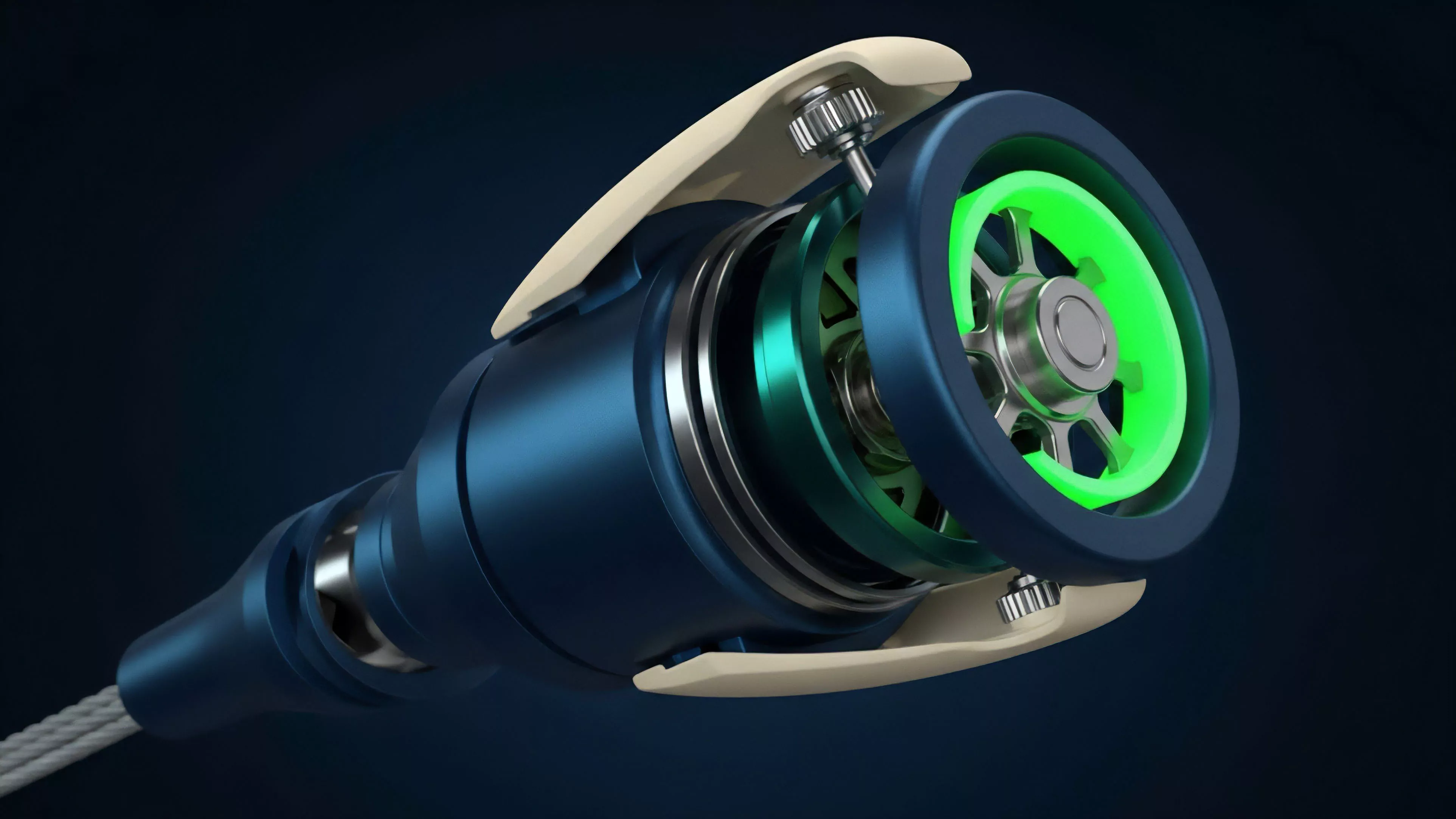

The architecture of ASIC Zero Knowledge Acceleration centers on the optimization of Modular Arithmetic and Elliptic Curve Cryptography. Proof generation requires performing millions of operations over large prime fields, a task for which traditional processors remain inefficient due to instruction set limitations and memory latency.

| Architecture Type | Performance Characteristic | Primary Application |

| General Purpose CPU | Flexible, High Latency | Basic Smart Contract Execution |

| GPU Acceleration | Parallel, Moderate Latency | Early Stage Proof Generation |

| ASIC Hardware | Specialized, Ultra-Low Latency | Production Grade ZK Proof Scaling |

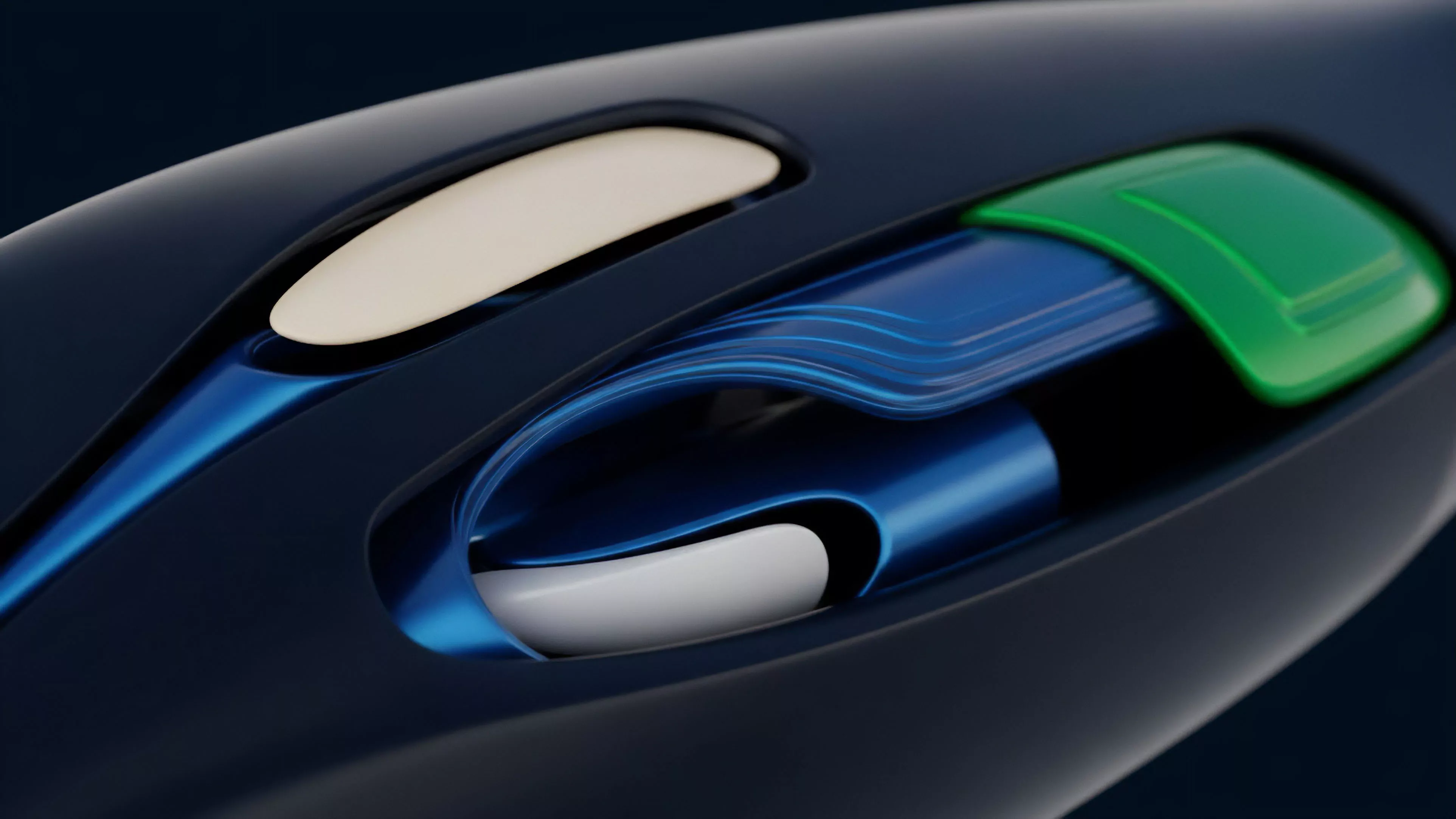

The theoretical framework involves designing hardware pipelines that minimize data movement between memory and logic units. By embedding the Finite Field Arithmetic directly into the silicon logic, these chips achieve a throughput density that exceeds general-purpose alternatives by several orders of magnitude. This is not about incremental speed improvements; it is about enabling entirely new categories of financial derivatives that require rapid, verifiable privacy.

The structural efficiency of ASIC Zero Knowledge Acceleration is defined by its ability to execute massive parallelization of modular arithmetic operations within a fixed power and latency budget.

Consider the parallel to high-frequency trading infrastructure, where the physical proximity of hardware to exchange matching engines dictates the profitability of arbitrage strategies. In this context, the ASIC serves as the physical manifestation of the protocol’s trust model, ensuring that the computational cost of privacy does not exceed the economic value of the trade.

Approach

Current deployment strategies for ASIC Zero Knowledge Acceleration focus on integrating these chips into decentralized validator sets and specialized Prover Networks. Market participants now utilize these circuits to lower the marginal cost of proof generation, thereby increasing the viability of complex financial instruments like private options and confidential order books.

- Prover Decentralization: Distributing the computational load across a network of specialized hardware providers ensures that no single entity monopolizes the validation process.

- Latency Reduction: Deploying hardware at the edge of the network minimizes the time between trade execution and cryptographic proof commitment.

- Cost Amortization: The high capital expenditure of silicon development is offset by the increased transaction volume enabled by the resulting speed improvements.

Financial institutions operating within these ecosystems must manage the risk of hardware obsolescence, as advancements in Zero Knowledge algorithms may require updated silicon designs. This reality forces a strategic alignment between protocol governance and hardware manufacturers to ensure that the physical infrastructure evolves in tandem with the cryptographic requirements of the market.

Evolution

The trajectory of ASIC Zero Knowledge Acceleration shows a transition from academic research to institutional-grade infrastructure. Early designs targeted specific proof systems, whereas modern approaches prioritize programmable, field-programmable gate array (FPGA) hybrids that allow for algorithmic agility while maintaining high performance. The market has moved from viewing these chips as luxury items to essential components for competitive decentralized exchanges.

Hardware-accelerated cryptography transforms privacy from a computational burden into a standard feature of high-performance financial market infrastructure.

This evolution mirrors the development of specialized financial trading hardware, where the focus shifted from software optimization to the physical design of network interface cards and ultra-low latency execution paths. The current phase involves the standardization of Proof Generation interfaces, allowing different protocols to leverage shared hardware resources, thus creating a more robust and liquid market for proof generation services.

Horizon

The future of ASIC Zero Knowledge Acceleration involves the integration of hardware-level privacy into the core of global settlement layers. As these circuits become cheaper and more widely available, we expect a rapid shift toward Confidential Computing environments where the underlying trade data remains hidden even from the validator nodes themselves. This will enable the creation of institutional-grade, privacy-preserving derivatives markets that satisfy both regulatory transparency requirements and individual participant confidentiality.

| Future Development | Systemic Impact |

| Hardware Level Proof Compression | Reduced Network Bandwidth Requirements |

| Integrated Secure Enclaves | Trustless Execution of Complex Derivatives |

| Global Prover Interoperability | Unified Liquidity Across Privacy Protocols |

The ultimate limit of this development is the seamless convergence of high-speed financial markets and absolute cryptographic privacy. The structural risks remain concentrated in the potential for centralization of prover power, necessitating ongoing research into permissionless and resilient hardware-software coordination mechanisms.