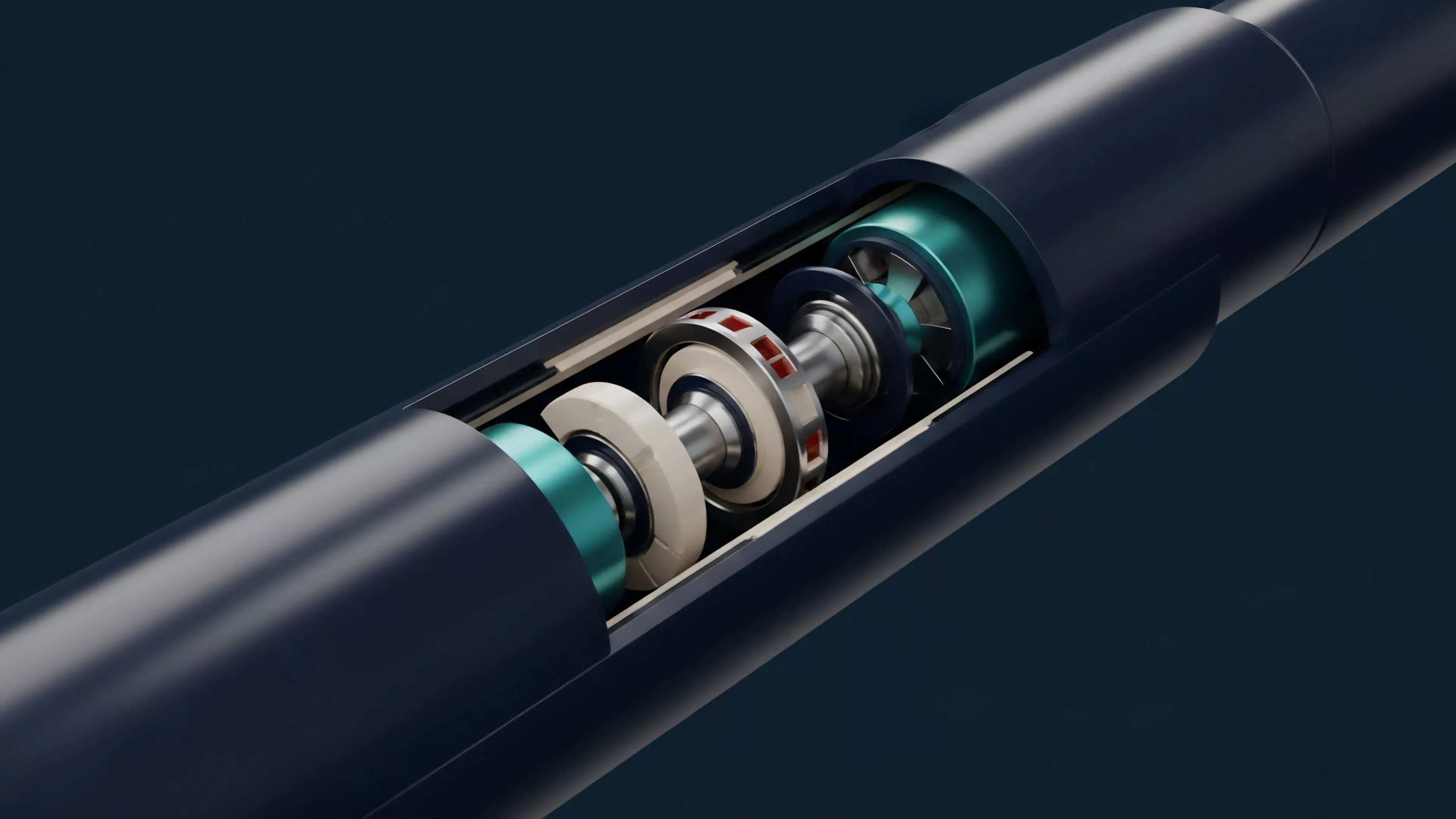

Low-Latency Execution

Meaning ⎊ Low-Latency Execution provides the technical speed required to capture price disparities and maintain market efficiency in decentralized finance.

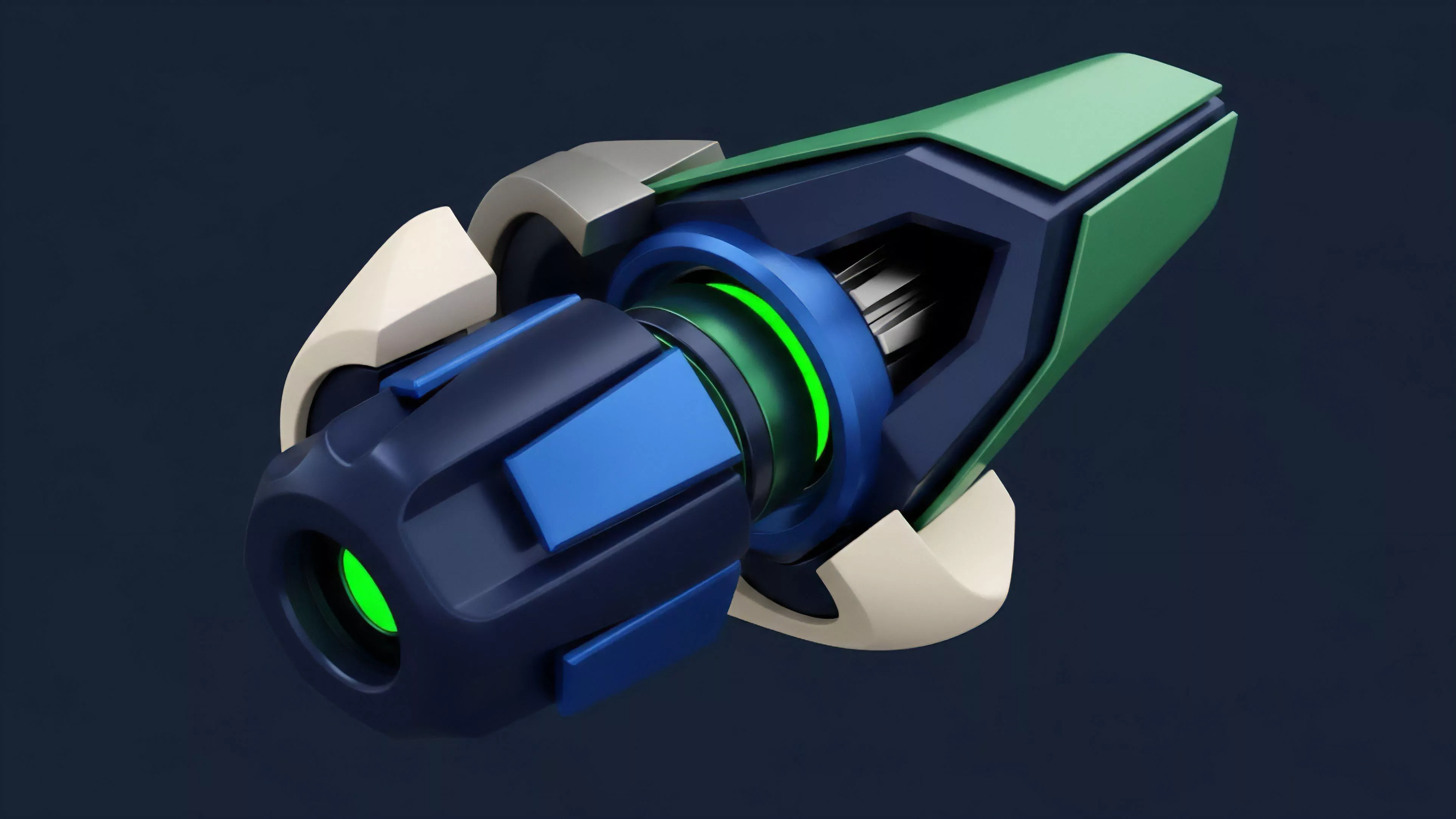

Off Chain Data Ingestion

Meaning ⎊ Off Chain Data Ingestion provides the essential cryptographic bridge for decentralized protocols to integrate real-time global financial market data.

Low Premium

Meaning ⎊ Option contracts priced cheaply due to low volatility or being deep out of the money, reflecting low probability of exercise.

Real Time Security Telemetry

Meaning ⎊ Real Time Security Telemetry provides the high-frequency data streams necessary to integrate protocol-level technical risks into dynamic pricing models.

Real Time Data Ingestion

Meaning ⎊ Real Time Data Ingestion provides the low-latency state synchronization required to maintain solvency and accurate pricing in decentralized markets.

Low-Latency Proofs

Meaning ⎊ Low-Latency Proofs enable instantaneous cryptographic verification of complex financial states, facilitating high-frequency decentralized trading.

ZK-Proof Finality Latency

Meaning ⎊ ZK-Proof Finality Latency measures the temporal lag between transaction execution and cryptographic settlement, defining the bounds of capital efficiency.

Proof Generation Latency

Meaning ⎊ Proof Generation Latency is the quantifiable time delay for cryptographic verification that dictates the risk window and capital efficiency of decentralized derivatives settlement.

Latency-Risk Trade-off

Meaning ⎊ The Latency-Risk Trade-off, or The Systemic Skew of Time, defines the non-linear exchange of execution speed for exposure to protocol-level and settlement uncertainty in crypto derivatives.

Settlement Latency

Meaning ⎊ Settlement Latency defines the temporal gap between trade execution and cryptographic finality, acting as a primary driver of systemic risk and capital inefficiency in decentralized derivative markets.

Proof Latency Optimization

Meaning ⎊ Proof Latency Optimization reduces the temporal gap between order submission and settlement to mitigate front-running and improve capital efficiency.