Zero-Knowledge Proof Libraries

Meaning ⎊ Zero-Knowledge Proof Libraries provide the cryptographic foundation for private, verifiable, and compliant transactions in decentralized finance.

Revenue Generation Models

Meaning ⎊ Revenue generation models transform crypto market volatility into sustainable protocol income through automated liquidity and risk management.

Idiosyncratic Alpha Generation

Meaning ⎊ Creating investment returns independent of general market trends through unique trading edges and information advantages.

Cryptographic Proof Generation

Meaning ⎊ Cryptographic proof generation provides the mathematical foundation for verifiable, private, and scalable decentralized financial derivatives.

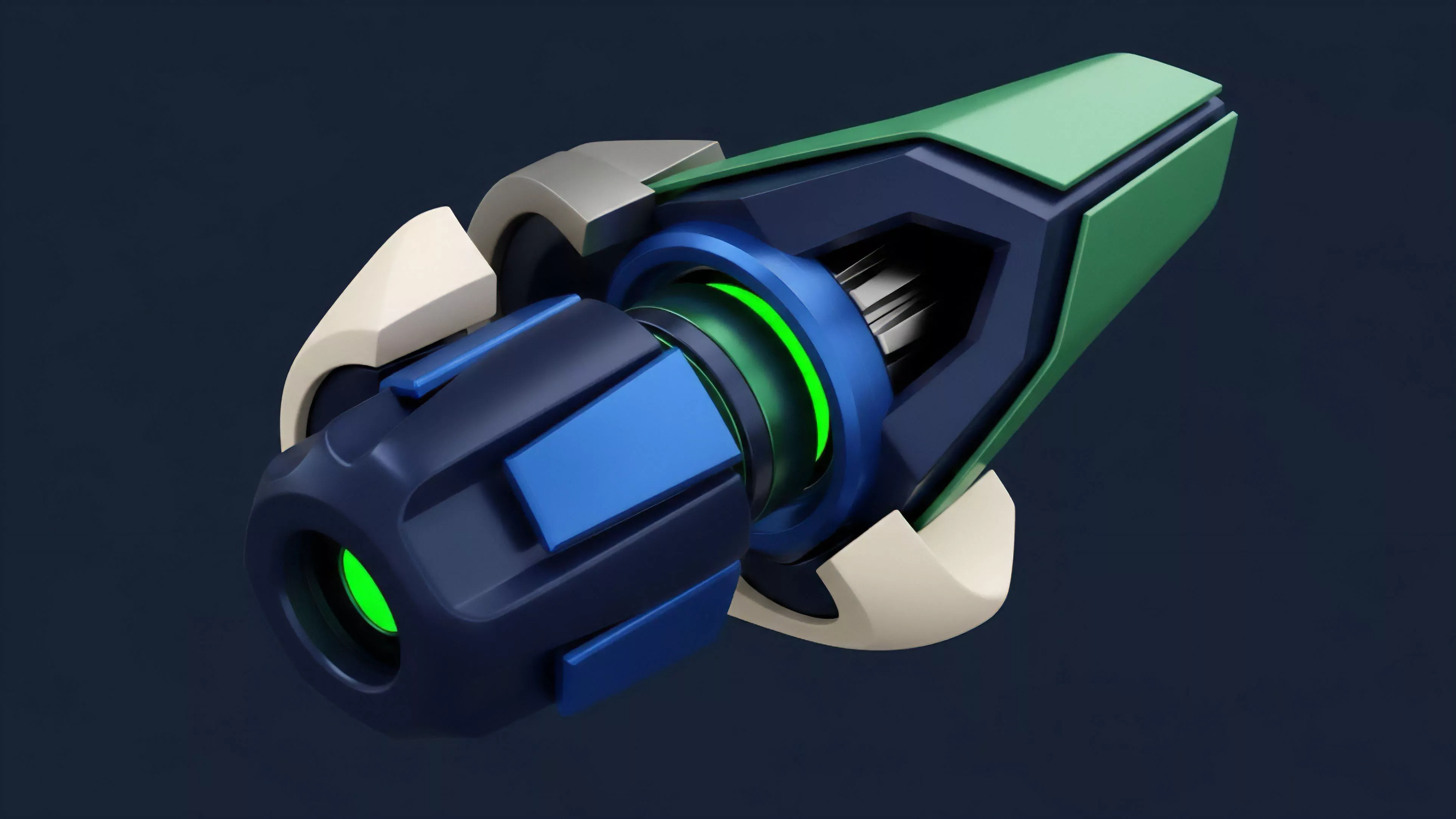

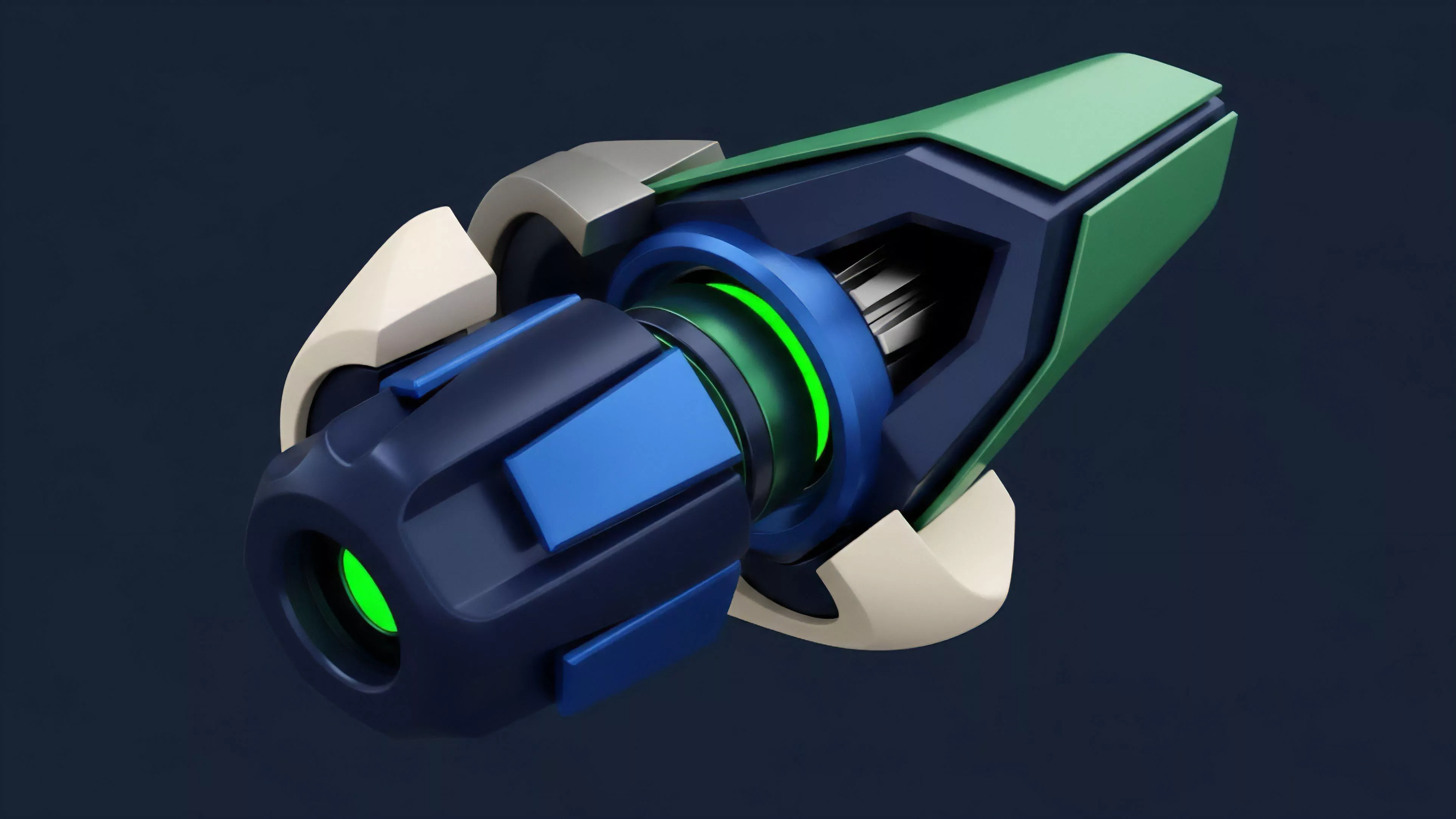

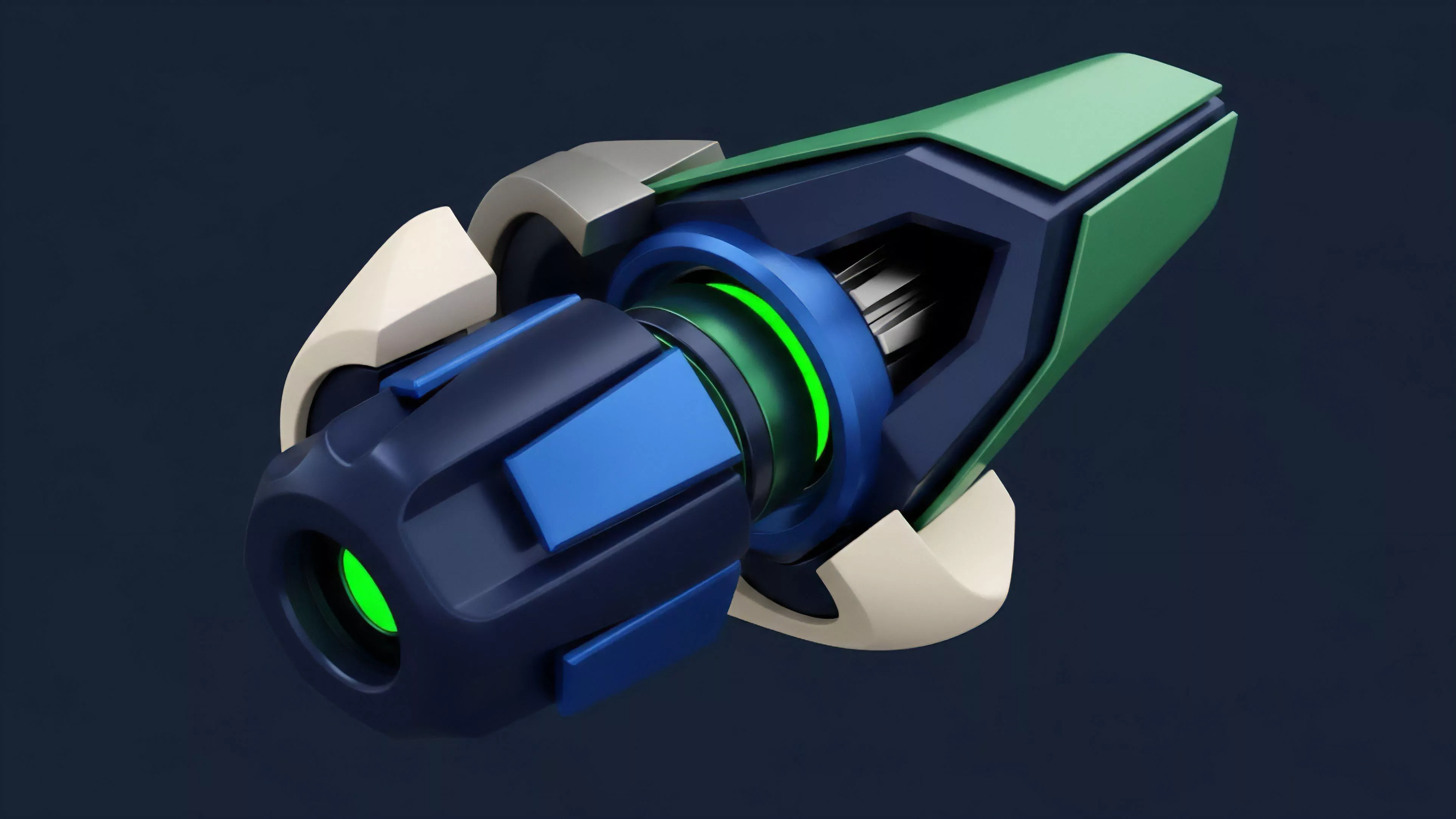

Zero-Knowledge Hardware

Meaning ⎊ Zero-Knowledge Hardware provides the essential computational throughput required to enable scalable, private, and high-frequency decentralized finance.

Real-Time Quote Generation

Meaning ⎊ Real-Time Quote Generation enables transparent, low-latency price discovery for decentralized derivatives by processing complex market data streams.

Hardware Depreciation

Meaning ⎊ The accounting process of allocating the declining value of physical mining assets over their useful economic life.

Zero-Knowledge Proof Reliability

Meaning ⎊ Zero-Knowledge Proof Reliability ensures the cryptographic integrity of off-chain financial state transitions within decentralized derivative markets.

Yield Generation Sustainability

Meaning ⎊ Long-term viability of returns from DeFi protocols, focusing on economic design and real revenue versus token incentives.

Revenue Generation

Meaning ⎊ Revenue generation in crypto options provides a mechanism for capturing volatility risk premiums through systematic, delta-neutral liquidity provision.

Trading Signal Generation

Meaning ⎊ Trading Signal Generation converts market entropy into precise execution mandates, enabling strategic capital allocation in decentralized derivatives.