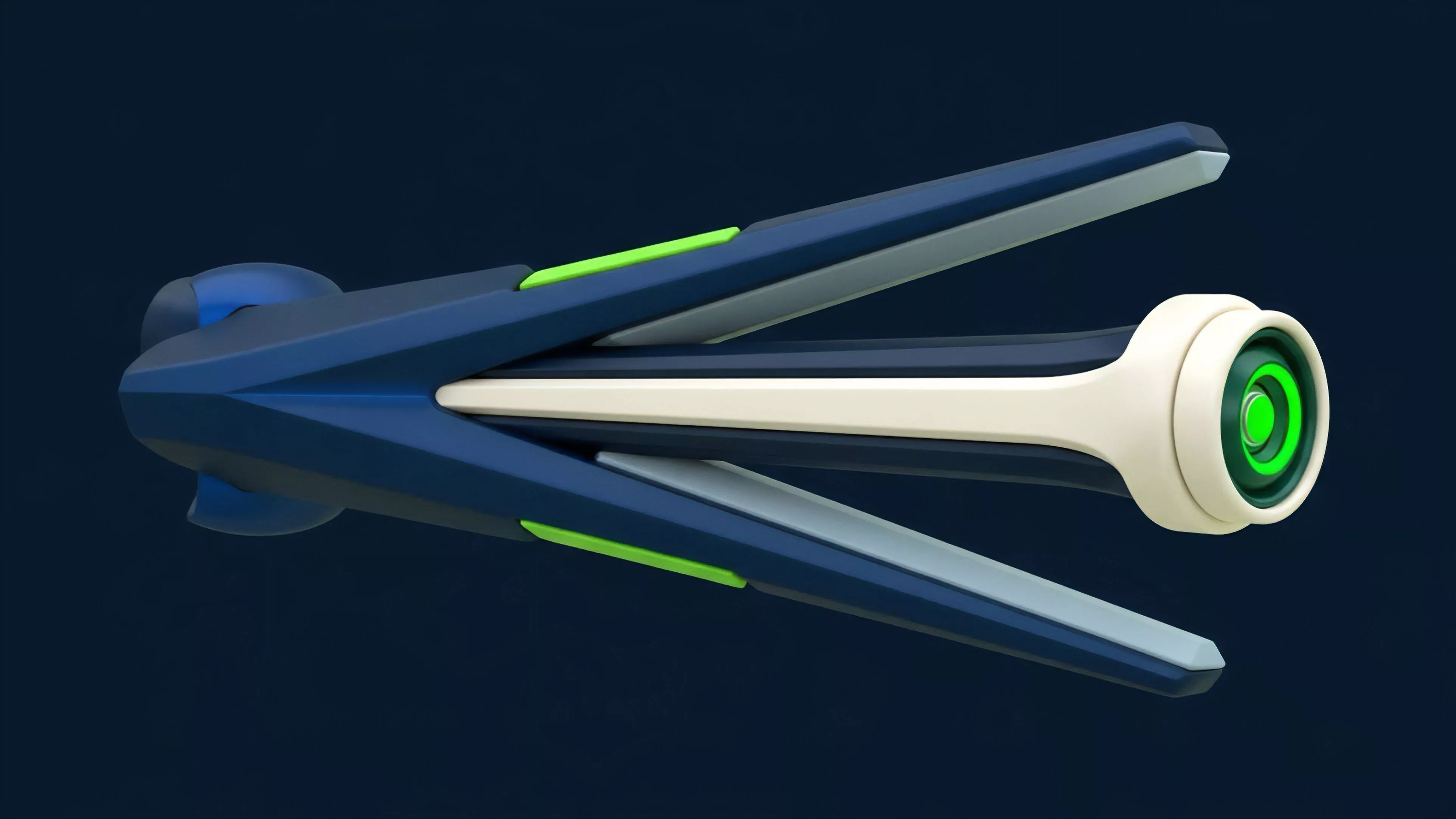

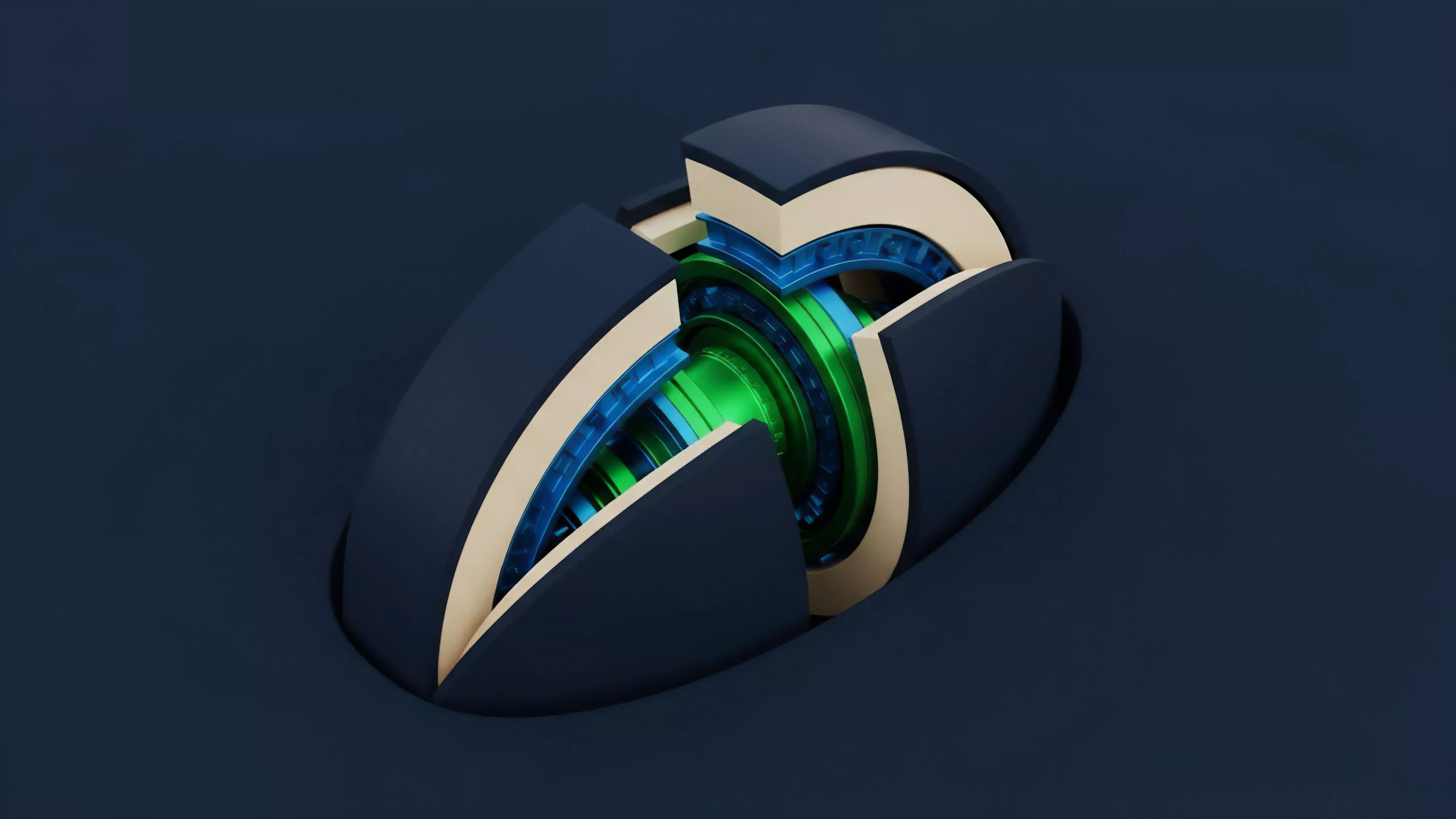

Hardware-Agnostic Proof Systems

Meaning ⎊ Hardware-Agnostic Proof Systems replace physical silicon trust with mathematical verification to secure decentralized financial settlement layers.

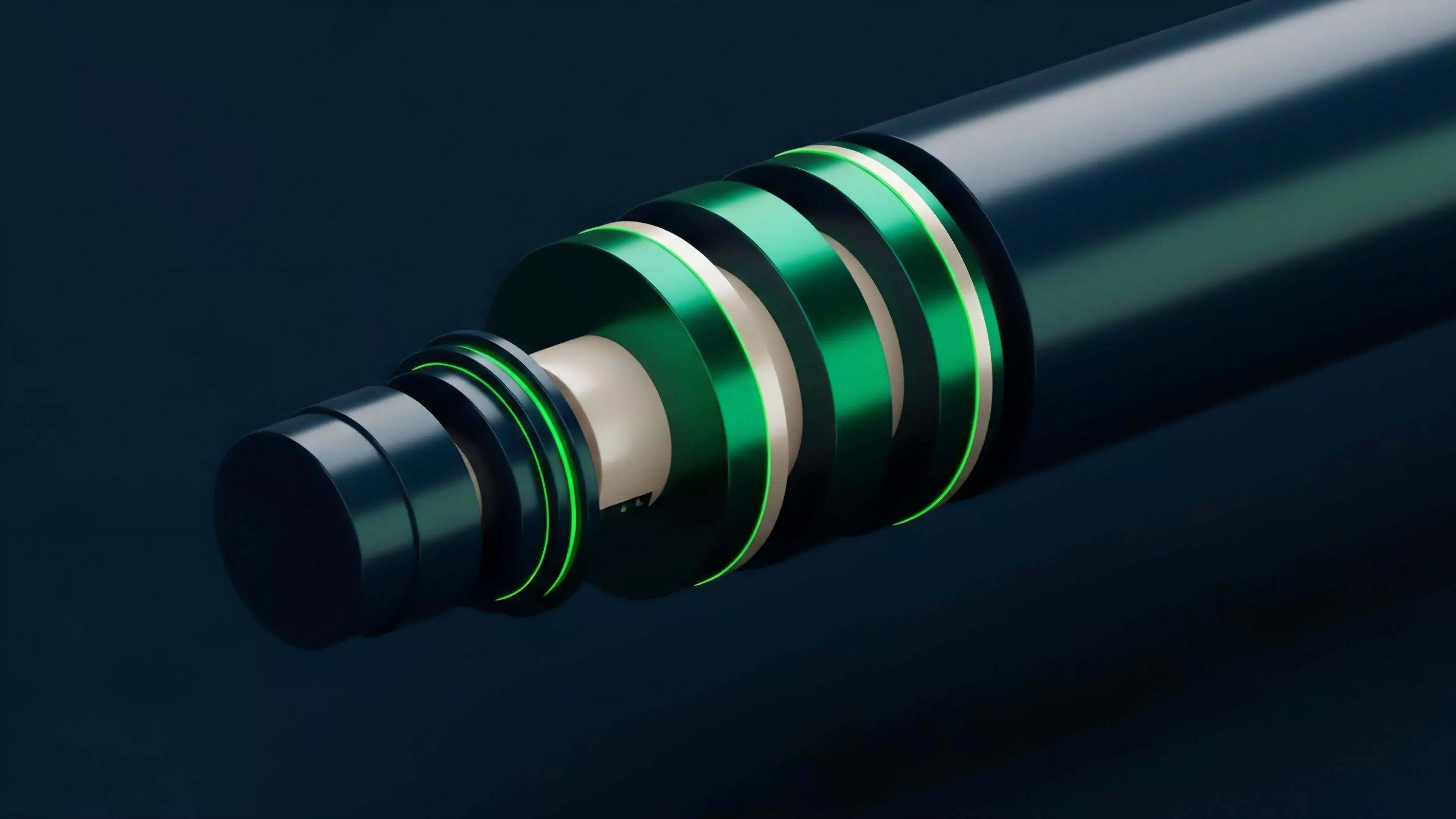

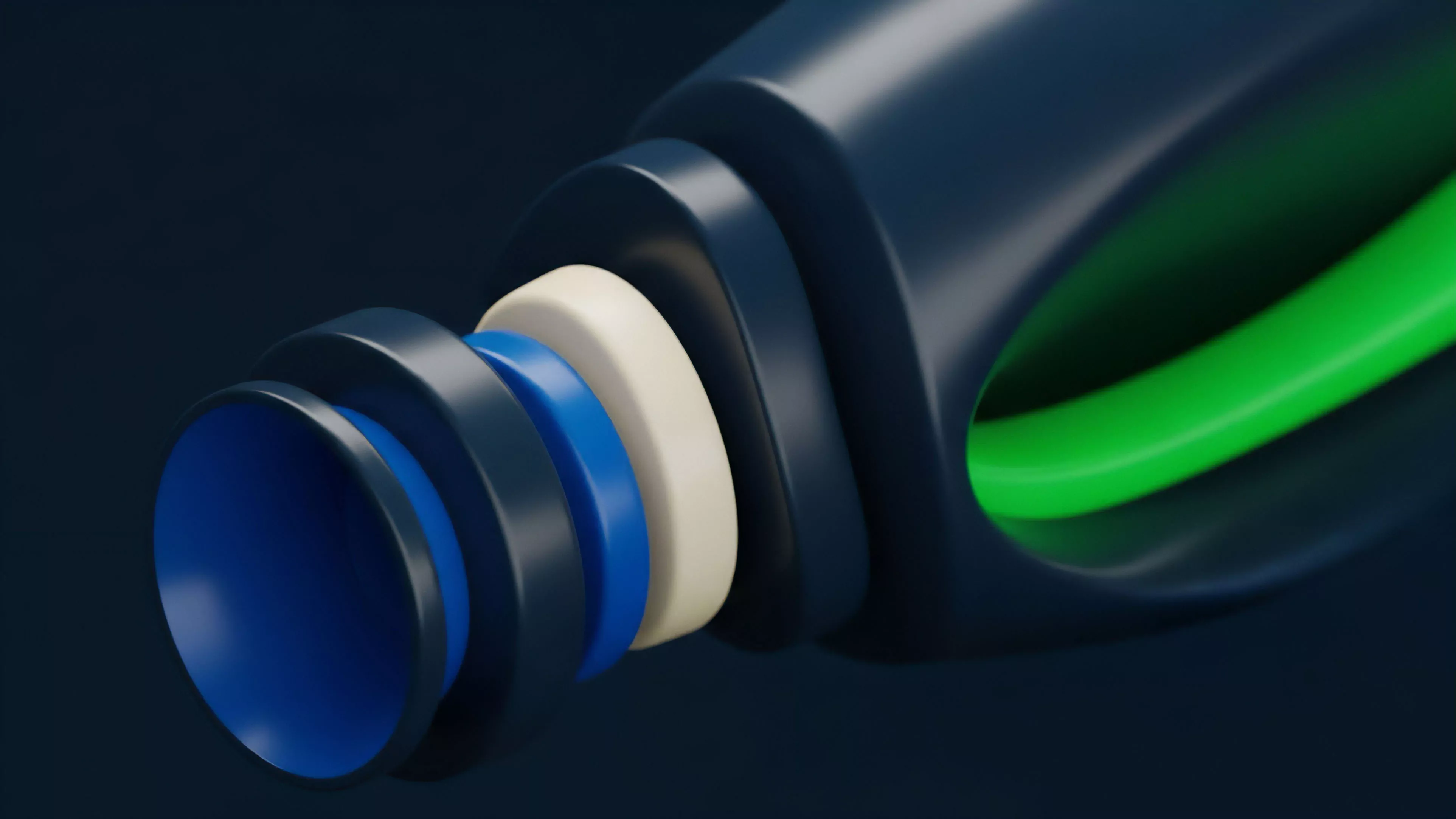

Hardware Security Modules

Meaning ⎊ Physical, tamper-resistant devices designed to store and manage cryptographic keys securely within isolated environments.

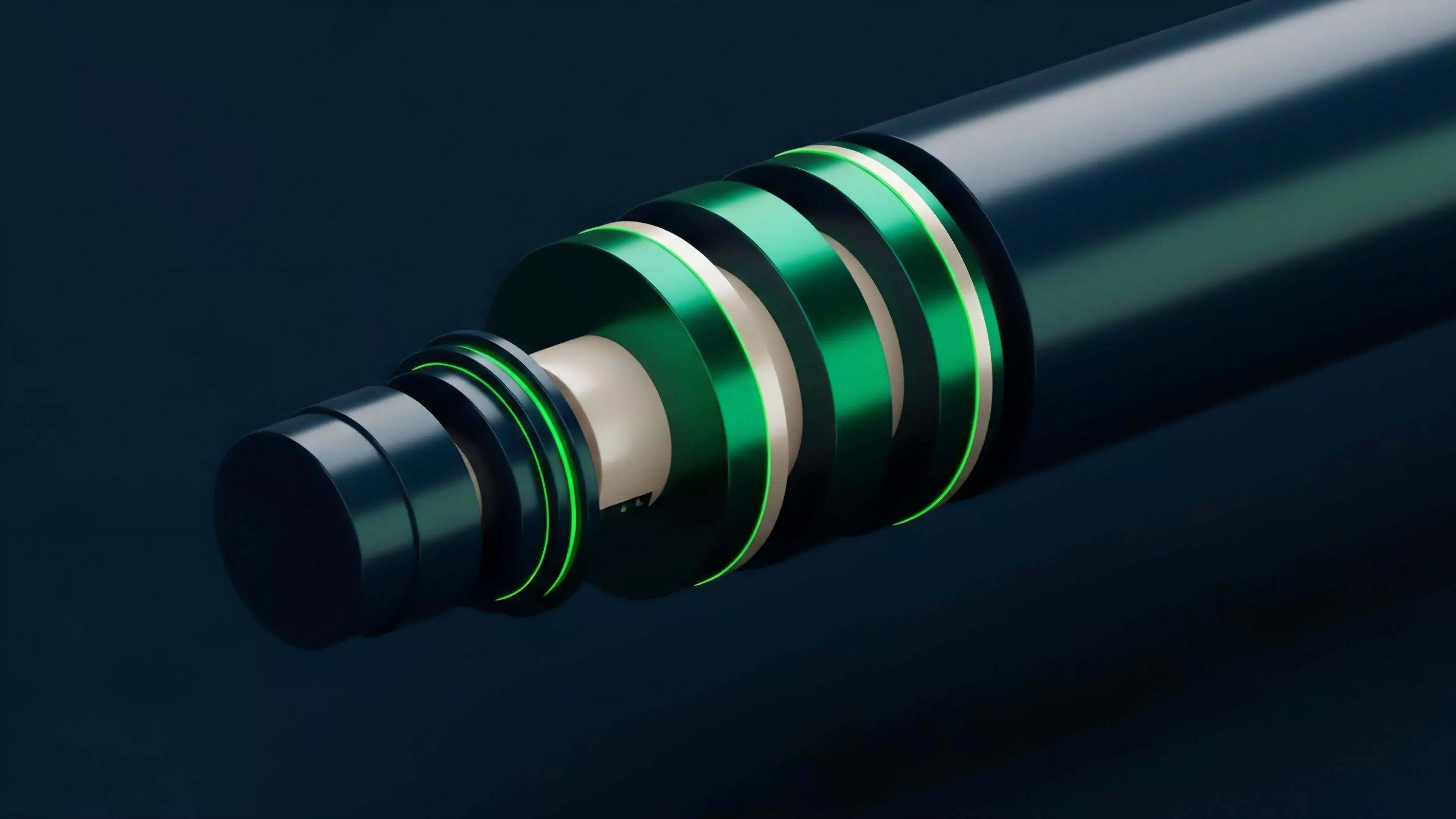

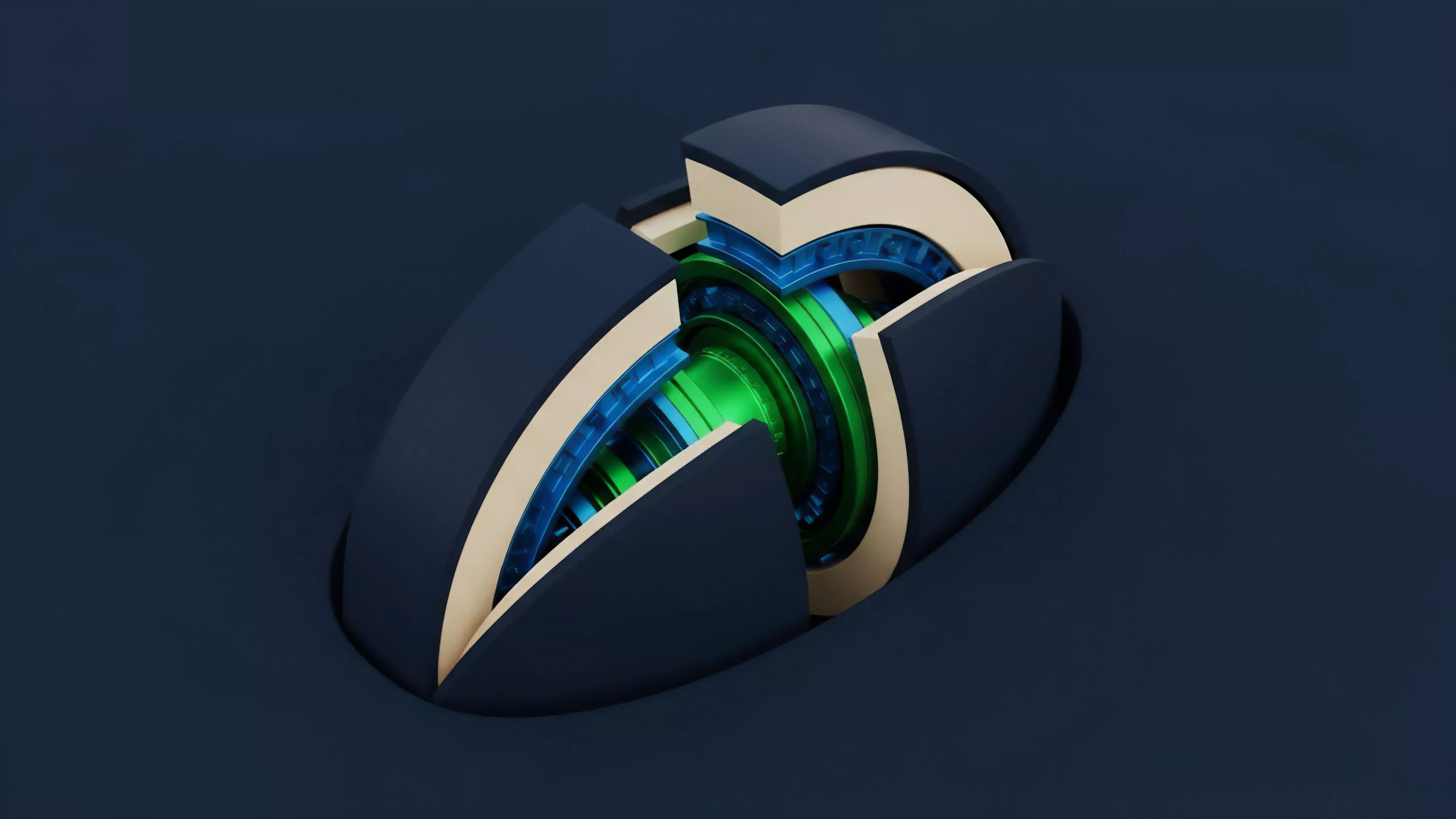

ZK SNARK Solvency Proof

Meaning ⎊ ZK SNARK Solvency Proof utilizes zero-knowledge cryptography to provide continuous, private, and mathematically certain verification of entity solvency.

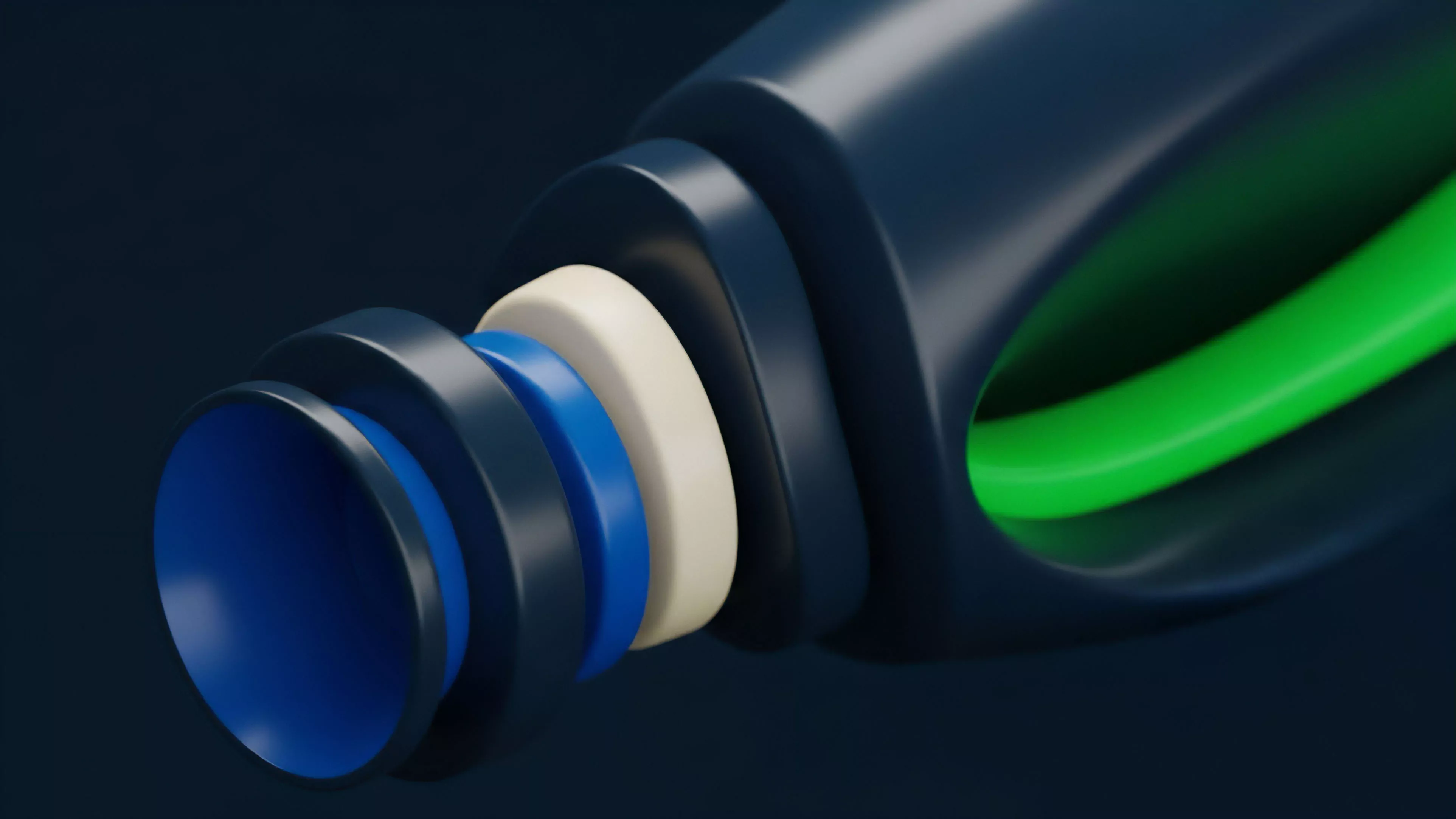

Hardware Acceleration

Meaning ⎊ Utilizing specialized hardware to perform high-speed computations and reduce latency in financial transactions.