Essence

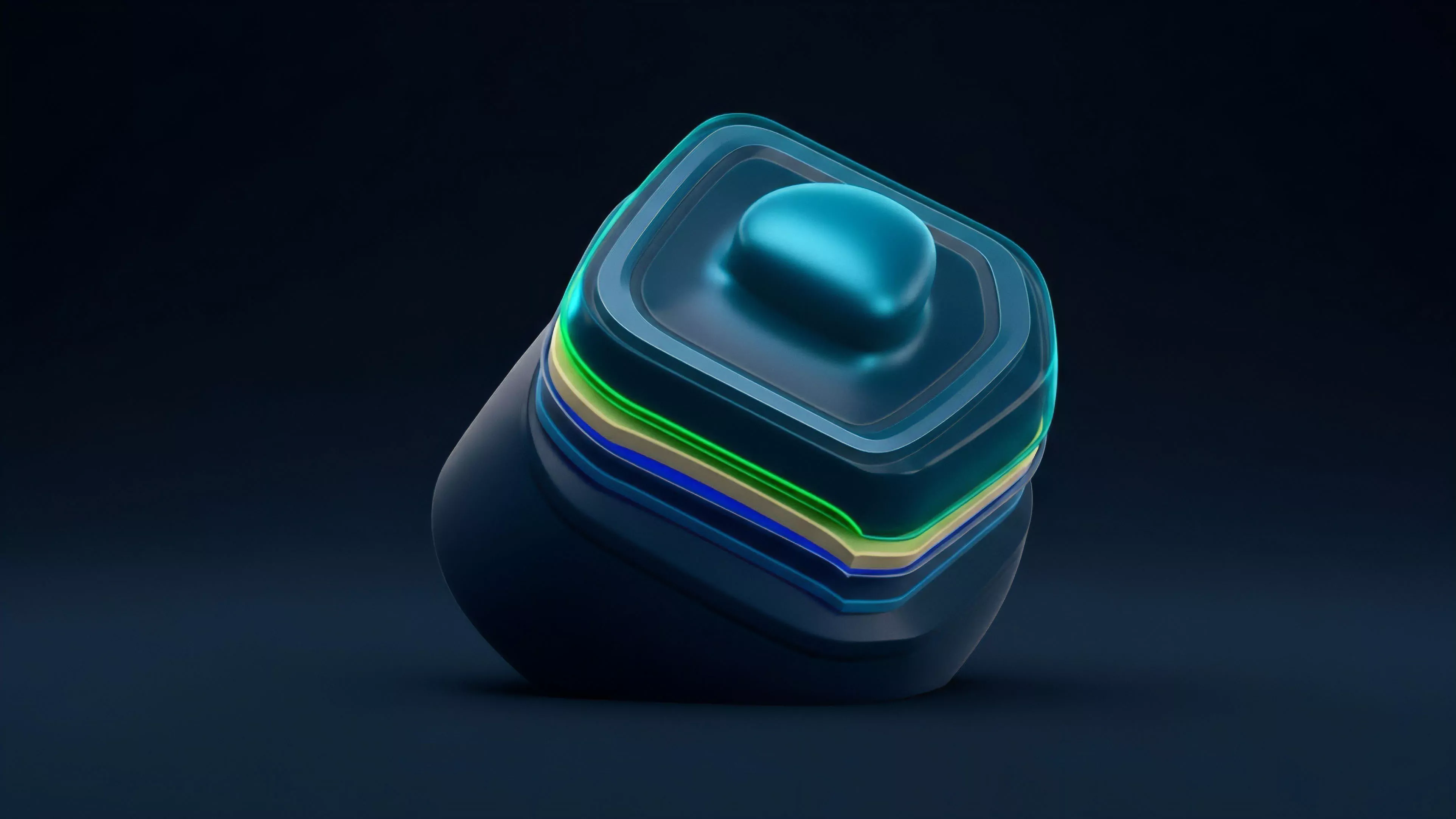

Zero Knowledge ASICs represent the hardware-level optimization of cryptographic proof generation. These application-specific integrated circuits target the computationally intensive process of creating succinct non-interactive arguments of knowledge, or SNARKs, which underpin the scalability and privacy of modern decentralized financial systems. By moving the heavy lifting of polynomial commitments and elliptic curve pairings from general-purpose CPUs or GPUs into dedicated silicon, these machines fundamentally alter the economics of block production and transaction verification.

Zero Knowledge ASICs function as the specialized compute layer required to compress complex state transitions into verifiable cryptographic proofs at scale.

The systemic relevance of these devices extends beyond mere speed. They act as a bottleneck and a gatekeeper for throughput in rollups and privacy-preserving protocols. When proof generation becomes efficient through specialized hardware, the cost per transaction drops, enabling new classes of financial derivatives that require high-frequency updates to a private or compressed state.

This hardware evolution shifts the competitive advantage from those holding general compute to those who possess the most efficient proof-generation architecture.

Origin

The lineage of Zero Knowledge ASICs traces back to the theoretical development of interactive proof systems and the subsequent transition to non-interactive, succinct proofs. Early implementations relied on general-purpose hardware, which proved insufficient for the recursive requirements of large-scale rollups. The industry faced a recurring problem: the latency of proof generation limited the frequency of state updates, effectively creating a ceiling for the throughput of layer-two scaling solutions.

- Cryptographic foundations established the mathematical necessity for efficient polynomial evaluations.

- Hardware limitations drove the initial search for parallelism in elliptic curve operations.

- Scaling requirements necessitated the transition from software-based provers to dedicated silicon circuits.

This trajectory mirrored the development of Bitcoin mining hardware, yet with a distinct shift in objective. While mining ASICs focus on hash rate competition for consensus security, these new circuits prioritize the speed of arithmetic circuit evaluation. The shift was accelerated by the growth of zero-knowledge rollups, which turned proof generation into a significant recurring cost for network operators.

This economic pressure transformed an academic curiosity into a commercial imperative for infrastructure providers.

Theory

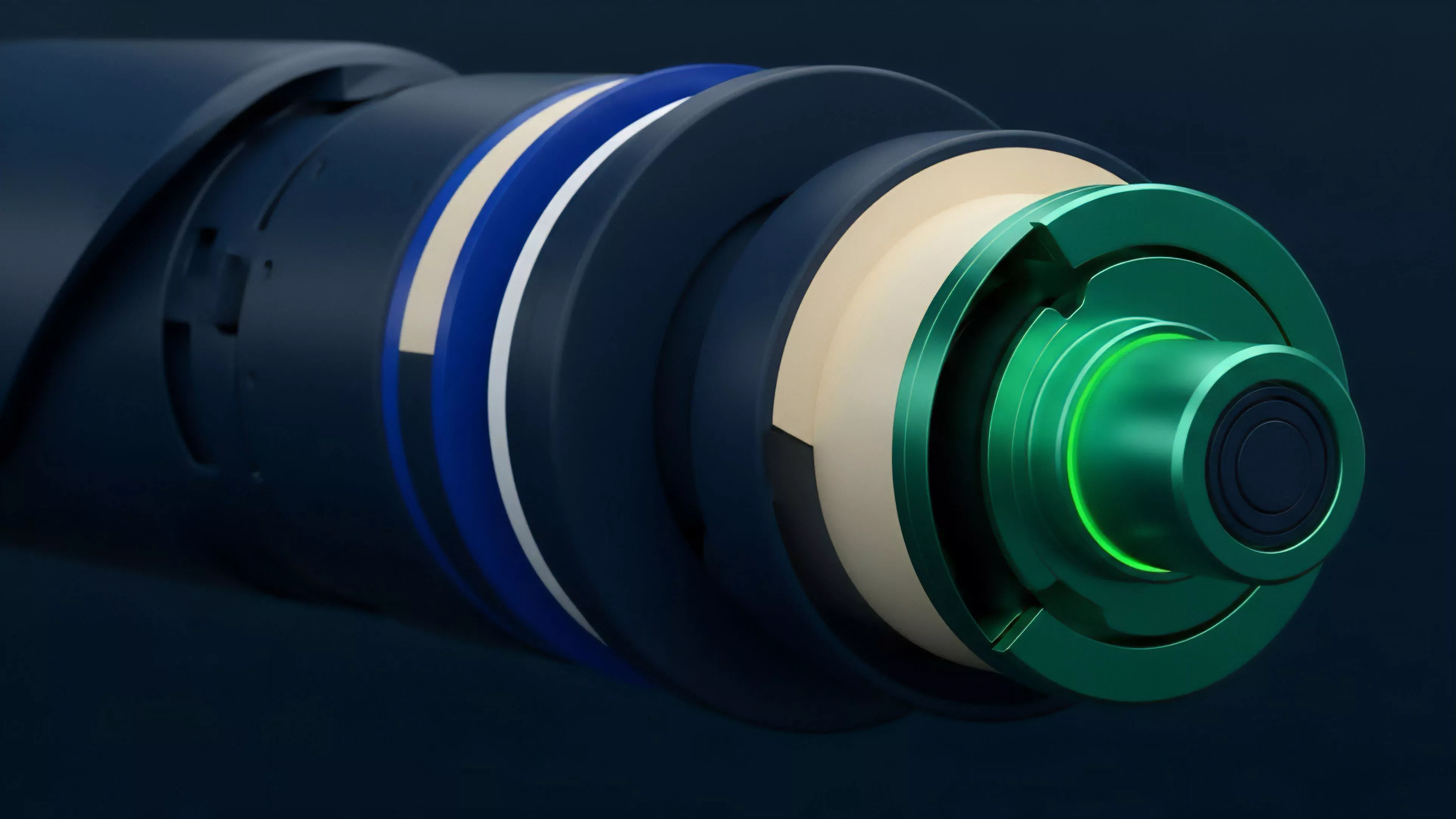

The architectural design of Zero Knowledge ASICs centers on accelerating the core arithmetic operations found in zero-knowledge proof systems. These systems generally involve massive multi-scalar multiplications and fast Fourier transforms over large finite fields. General-purpose processors struggle with these tasks due to their high memory access requirements and branch-heavy execution patterns.

The efficiency of Zero Knowledge ASICs is determined by the hardware ability to perform high-throughput field arithmetic while minimizing data movement between memory and compute units.

| Component | Functional Role |

| Field Arithmetic Unit | Executes modular addition and multiplication |

| Memory Controller | Manages high-bandwidth data streaming |

| Pipeline Logic | Optimizes instruction throughput for SNARK circuits |

The mathematical models underlying these circuits often involve optimizing the NTT or number theoretic transform. By hard-coding the field parameters, designers eliminate the overhead of programmable instruction sets. This specialization allows for a dramatic reduction in power consumption per proof generated, which is the primary driver of profitability for operators of prover networks.

The interaction between the circuit architecture and the specific proof system, such as PLONK or Groth16, creates a deep coupling between software standards and hardware deployment.

Approach

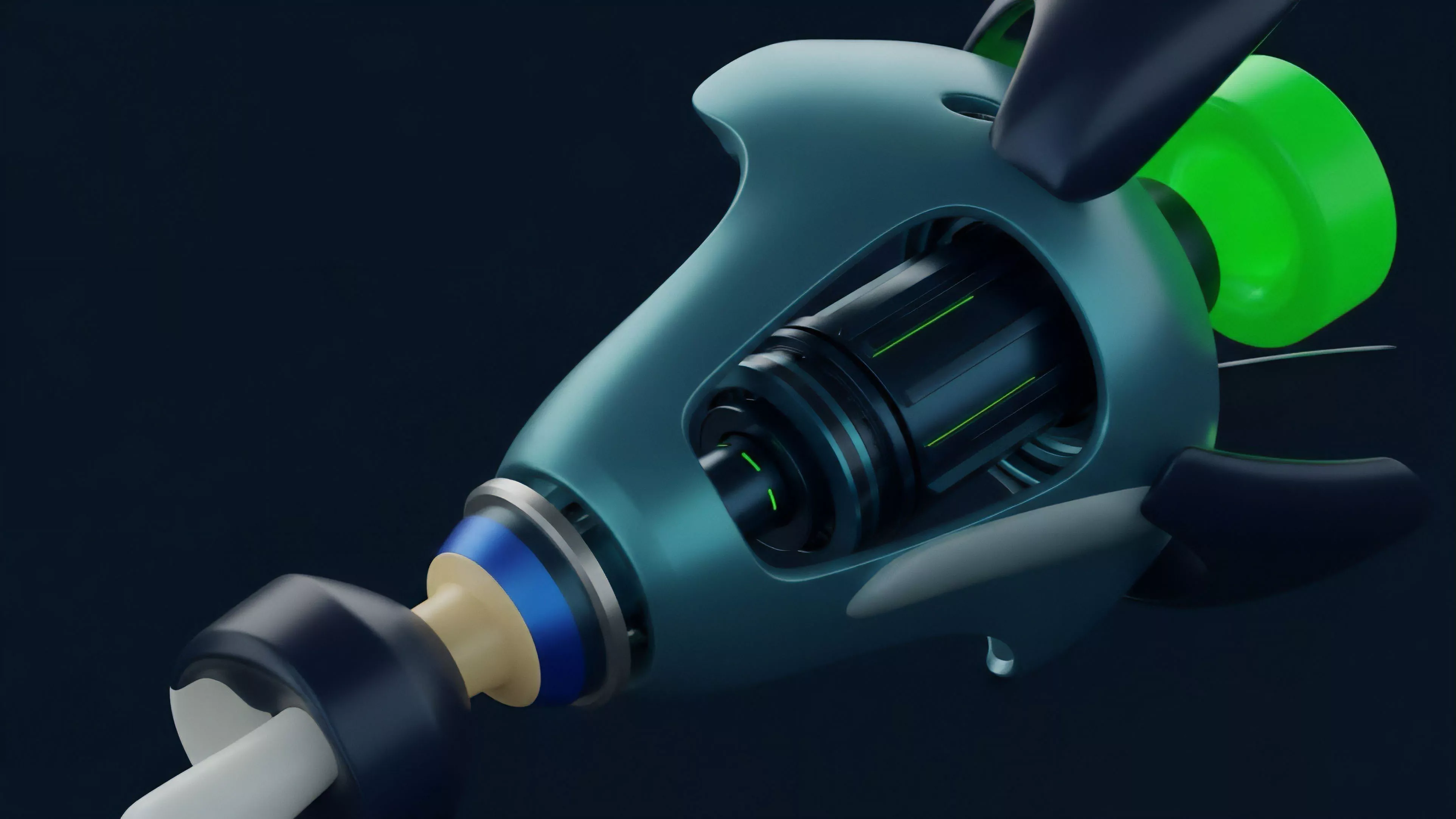

Current strategies for deploying Zero Knowledge ASICs involve balancing hardware specialization with the risk of rapid protocol upgrades. Because zero-knowledge proof systems remain in a state of constant refinement, hard-coding a circuit for a specific version carries the risk of obsolescence. Prover networks currently utilize a hybrid approach, combining FPGA-based flexibility with the raw performance of full-custom ASIC designs.

- Hardware abstraction layers allow protocols to interact with different prover architectures through standardized APIs.

- Decentralized prover markets facilitate the competitive allocation of proof generation tasks to the most efficient hardware available.

- Recursive proof aggregation reduces the total load on individual provers, allowing for more granular hardware utilization.

This environment functions as a high-stakes game where participants must predict the evolution of cryptographic standards. Those who bet on the wrong curve or proof system face stranded capital. The financial strategy centers on minimizing the cost per proof, which directly correlates to the competitive position of a rollup within the broader decentralized market.

Efficiency here is not a luxury but a requirement for protocol survival, as higher prover costs inevitably lead to higher user fees and reduced liquidity.

Evolution

The market for Zero Knowledge ASICs has moved from initial prototyping by academic teams to significant capital allocation by specialized hardware firms. Early iterations focused on simple proof verification, whereas modern designs target the full generation pipeline. This shift reflects the broader maturation of the rollup sector, which now requires robust, high-availability infrastructure rather than experimental testnets.

The transition from software-based provers to ASIC-driven networks represents a shift from collaborative compute to competitive industrial-scale infrastructure.

We are witnessing a consolidation of hardware standards, similar to the historical development of GPU acceleration for machine learning. The volatility of the underlying crypto assets creates a complex risk profile for these hardware providers. If the throughput demands of a protocol fail to materialize, the specialized nature of the ASICs prevents their repurposing for other tasks.

This structural risk forces firms to align closely with specific blockchain ecosystems, creating deep dependencies between the hardware manufacturers and the layer-two protocol developers.

Horizon

The future of Zero Knowledge ASICs lies in the integration of hardware-level support for fully homomorphic encryption and more complex recursive proof structures. As protocols move toward greater decentralization, the prover role will likely become a commoditized service, similar to current cloud computing infrastructure. The ultimate goal is the democratization of proof generation, where even mobile devices might eventually participate in lightweight proof validation or generation.

| Phase | Primary Driver |

| Integration | Rollup throughput requirements |

| Commoditization | Market-wide prover competition |

| Universalization | Hardware-native privacy and scaling |

This evolution will redefine the limits of what is possible in decentralized finance. By removing the cost barrier to cryptographic proof generation, we enable real-time, private, and trustless financial transactions at a global scale. The bottleneck will shift from hardware availability to the efficiency of the underlying cryptographic algorithms themselves. The winners in this space will be those who bridge the gap between abstract mathematical proofs and the physical reality of high-performance, low-power silicon architecture.