Essence

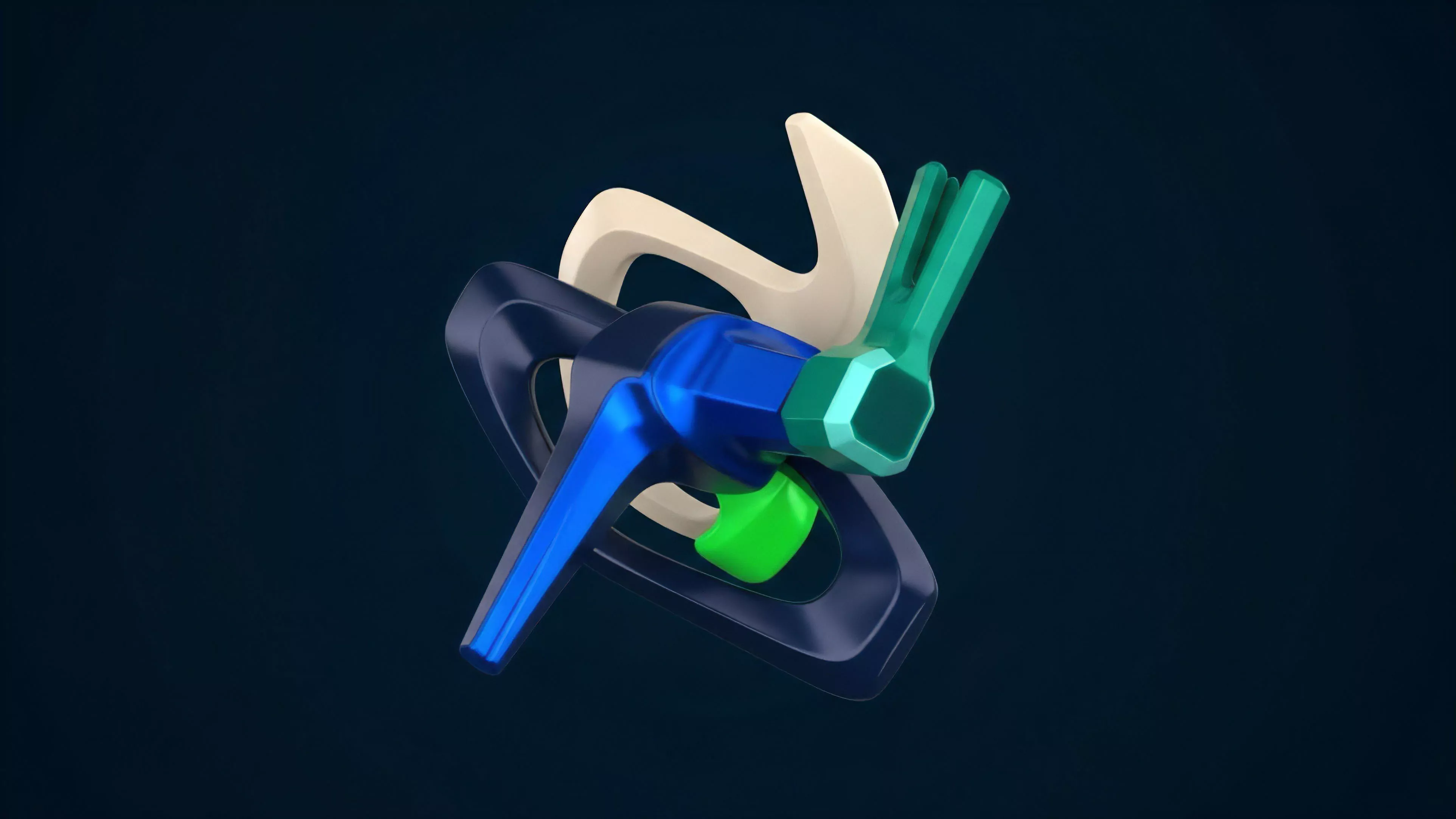

Secure Hardware Design refers to the integration of cryptographic primitives directly into physical silicon to ensure the integrity, confidentiality, and authenticity of digital assets. This architecture moves trust from volatile software environments to immutable physical circuits. By embedding keys within isolated hardware enclaves, the design prevents unauthorized extraction, even when the host operating system faces compromise.

Secure Hardware Design anchors digital value in physical silicon to ensure cryptographic integrity against software-based adversarial attacks.

The functional significance lies in the creation of a hardware-based root of trust. Financial systems utilizing this approach achieve resilience against remote memory dumping or kernel-level exploits that typically threaten software-only wallets. The architecture establishes a boundary where sensitive operations, such as private key signing, occur within a tamper-resistant execution environment, shielding them from the broader network surface.

Origin

The genesis of Secure Hardware Design within crypto finance traces back to the necessity of solving the cold storage problem.

Early practitioners recognized that storing private keys on connected computers invited catastrophic risk. This realization drove the development of specialized hardware security modules and hardware wallets designed to isolate signing operations from internet-facing environments.

- Hardware Security Modules originated in enterprise data centers to manage cryptographic keys securely.

- Hardware Wallets adapted these principles to individual user control, introducing the concept of air-gapped signing.

- Trusted Execution Environments evolved to provide secure enclaves within general-purpose processors.

These developments represent a shift toward physical defense-in-depth strategies. By separating the signing device from the transaction broadcast device, architects effectively reduced the attack vector for individual and institutional participants. The movement sought to eliminate the reliance on potentially malicious software layers, placing the security burden on the physical integrity of the device itself.

Theory

The theoretical framework rests on the principle of isolation.

Secure Hardware Design relies on creating a secure enclave ⎊ a physically and logically separated portion of the processor ⎊ where sensitive data resides and computations occur. Adversaries attempting to intercept these operations encounter physical barriers rather than software hooks.

| Metric | Software-Only Security | Hardware-Anchored Security |

| Key Exposure | High (Memory Dumps) | Negligible (Physical Tampering Required) |

| Execution | Shared OS Space | Isolated Enclave |

| Trust Basis | Code Logic | Physical Circuitry |

The mathematical modeling of these systems incorporates side-channel analysis, where researchers study power consumption and electromagnetic emissions to detect potential leaks. Designing against these vectors requires constant time execution and power-blind operations, ensuring that the duration or energy usage of a cryptographic function does not reveal information about the secret key being processed.

Hardware-anchored security relies on physical isolation to prevent side-channel leakage and unauthorized access to cryptographic primitives.

This domain demands an understanding of hardware-level vulnerabilities, such as rowhammer attacks or speculative execution flaws. The systems architect views the processor as an adversarial environment where every gate must be scrutinized for potential leaks. Logic paths are constrained to minimize exposure, creating a deterministic environment where the probability of successful key exfiltration remains mathematically bounded by the physical cost of device destruction.

Approach

Current implementations of Secure Hardware Design prioritize a layered defense strategy.

Developers utilize field-programmable gate arrays or application-specific integrated circuits to create custom cryptographic pipelines. This approach allows for the hardware-level implementation of elliptic curve cryptography, ensuring that signing operations remain shielded from software-based interceptors.

- Physical Unclonable Functions generate unique cryptographic identifiers based on microscopic manufacturing variations in silicon.

- Secure Boot Protocols verify the integrity of firmware before execution, preventing the loading of malicious code.

- Tamper Detection Sensors trigger automatic key erasure upon physical intrusion or extreme environmental stress.

Market participants now demand institutional-grade custody solutions that integrate these hardware primitives. The current focus centers on multi-party computation combined with hardware isolation. By distributing shares of a key across different secure hardware modules, firms minimize the impact of a single device compromise, achieving a higher standard of systemic stability.

Evolution

The transition from simple cold storage devices to sophisticated hardware security modules reflects a broader shift toward systemic risk mitigation.

Initially, hardware solutions served individuals, but the rise of decentralized finance required solutions for automated, high-frequency settlement. Modern designs incorporate hardware-accelerated consensus validation, allowing for rapid, secure transaction signing in permissionless environments.

Evolutionary progress in hardware security moves from static storage devices toward high-performance, enclave-based transaction validation engines.

The integration of Secure Hardware Design into decentralized protocols remains a subject of intense research. As liquidity pools grow, the need for hardware-backed oracle nodes and validator infrastructure becomes paramount. Systems are evolving to support remote attestation, where a device provides cryptographic proof of its internal state to the blockchain, enabling verifiable execution of financial contracts without trusting the operator.

The architecture has matured to handle the complexity of programmable money. We no longer treat hardware as a vault but as an active participant in the consensus mechanism. This change creates new possibilities for automated risk management where the hardware itself enforces liquidation thresholds or margin requirements based on pre-programmed logic, effectively turning the silicon into a decentralized judge of financial state.

Horizon

The future of Secure Hardware Design points toward the complete elimination of human intervention in key management.

We anticipate the widespread adoption of hardware-level threshold signatures, where signing keys never exist in a complete state, even within a single enclave. Instead, distributed hardware nodes compute partial signatures, providing a robust defense against localized failures.

| Future Direction | Systemic Implication |

| On-Chain Attestation | Verified Execution Transparency |

| Threshold Hardware | Elimination Single Points Failure |

| Silicon-Level Governance | Hard-Coded Protocol Enforcement |

The intersection of quantum-resistant cryptography and Secure Hardware Design will define the next cycle. Preparing for post-quantum algorithms requires a redesign of existing hardware accelerators, as the computational requirements for these primitives differ significantly from current standards. Architects must build flexible, upgradeable hardware platforms that can adapt to evolving cryptographic requirements without compromising the physical root of trust. The ultimate trajectory leads to a financial system where hardware integrity serves as the final arbiter of truth. By embedding economic rules into physical silicon, we create systems that operate independently of human discretion, reducing the reliance on intermediaries and building a more resilient foundation for decentralized markets.