Essence

Hardware Security Architecture represents the foundational layer of cryptographic trust, moving beyond software-based abstractions to embed security primitives directly into physical silicon. By leveraging specialized circuits such as Trusted Execution Environments and Hardware Security Modules, this architecture ensures that sensitive cryptographic keys, private signing operations, and transaction validation logic remain isolated from the primary operating system.

Hardware Security Architecture provides the physical bedrock for decentralized financial integrity by isolating cryptographic operations from host system vulnerabilities.

The systemic relevance lies in its ability to enforce non-repudiation and integrity in environments where the host OS is potentially compromised. When dealing with decentralized derivatives, this architecture serves as the ultimate arbiter of truth, ensuring that signing agents remain impervious to memory-scraping attacks or kernel-level tampering.

Origin

The lineage of Hardware Security Architecture traces back to early research in tamper-resistant computing and the development of Smart Cards. These initial implementations sought to provide a portable, secure storage mechanism for personal identification and basic financial transactions.

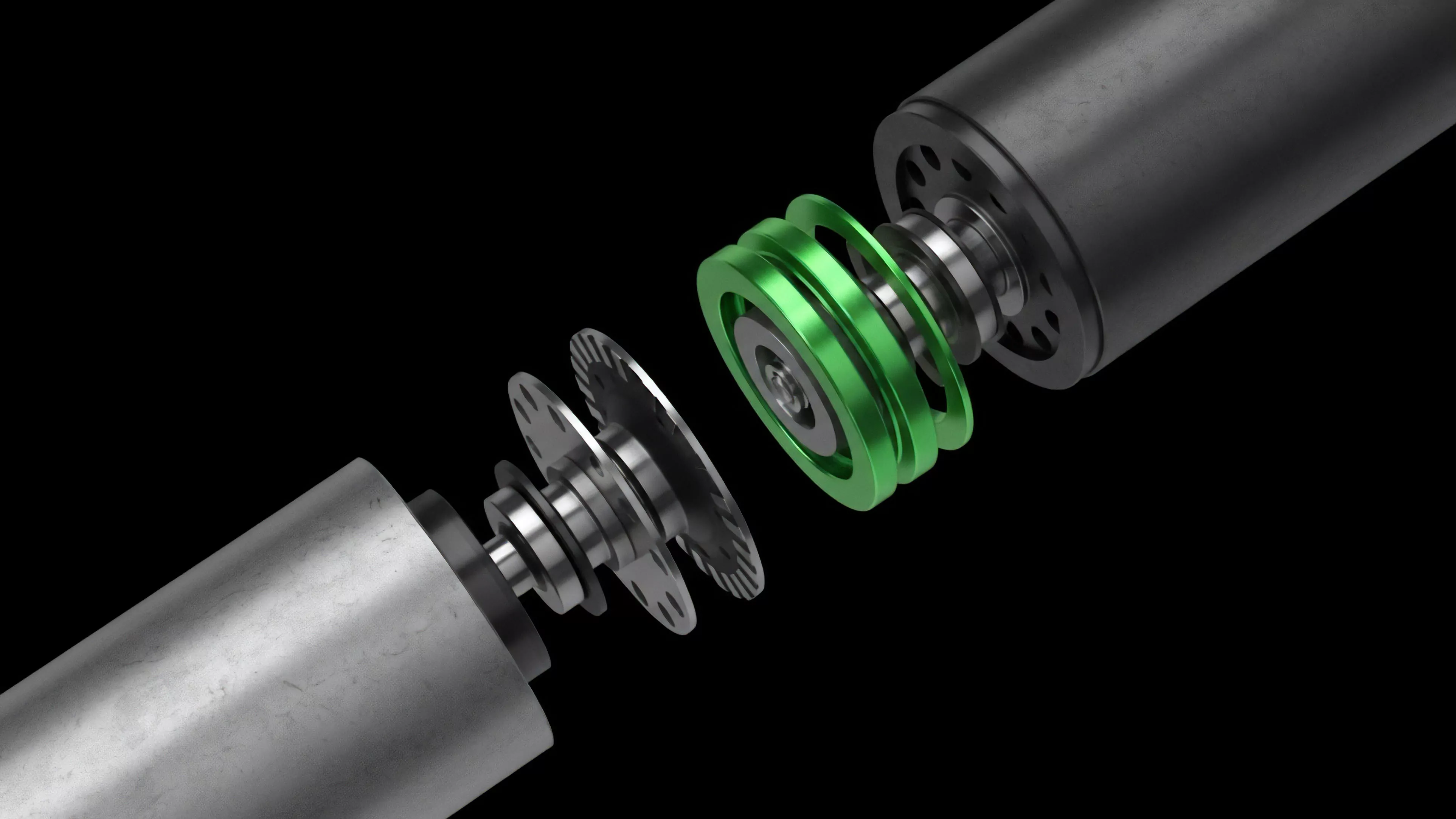

As the industry progressed, the need for high-performance cryptographic acceleration led to the design of dedicated Hardware Security Modules capable of handling complex asymmetric key generation and signing processes.

- Trusted Platform Modules emerged to provide a standardized, motherboard-integrated root of trust for system integrity verification.

- Secure Elements evolved from mobile telephony security to become the standard for consumer-grade cryptographic asset protection.

- Hardware Security Modules transitioned from centralized data center infrastructure to become specialized hardware accelerators for high-frequency institutional trading.

This evolution was driven by the inherent fragility of software-defined security. Developers recognized that if the underlying machine state is manipulated, all higher-level cryptographic proofs become unreliable, leading to the adoption of physically enforced boundaries as the primary defensive strategy.

Theory

The theoretical framework of Hardware Security Architecture rests upon the concept of Root of Trust. This principle dictates that security must be anchored in a component that is inherently trustworthy, immutable, and physically shielded.

In the context of crypto derivatives, this means the signing engine exists in a state of operational autonomy, separated from the general-purpose compute environment.

A robust Root of Trust ensures that cryptographic secrets remain physically inaccessible even when the primary execution environment is fully compromised.

Mathematical modeling of these systems often employs the Adversarial Capacity Analysis, which measures the work factor required for an attacker to extract key material from the physical device. Unlike software protocols that rely on code logic, this architecture relies on physical constraints such as power analysis resistance, electromagnetic shielding, and laser-glitch protection.

| Architecture Type | Isolation Level | Performance Impact |

|---|---|---|

| Software Wallet | None | Negligible |

| Trusted Execution Environment | Moderate | Low |

| Hardware Security Module | High | Significant |

The systemic implications involve a trade-off between throughput and security. While Hardware Security Modules offer superior protection, their latency profiles can hinder high-frequency market-making operations. Therefore, the design challenge involves balancing physical isolation with the need for low-latency order flow execution.

Approach

Current implementations prioritize the deployment of Secure Elements and Trusted Execution Environments to facilitate secure interaction with decentralized protocols.

Modern market participants utilize these architectures to manage multi-signature schemes and automated derivative execution. The process involves delegating the signing authority to a dedicated hardware path, ensuring that the private key never touches the main memory of the application server.

- Secure Enclaves allow for the execution of sensitive code in a protected memory space, preventing even privileged OS processes from inspecting the execution flow.

- Hardware-Accelerated Signing reduces the time required for complex cryptographic proofs, enabling faster settlement cycles in volatile markets.

- Physical Tamper Detection triggers immediate key destruction upon detecting unauthorized chassis opening or environmental manipulation.

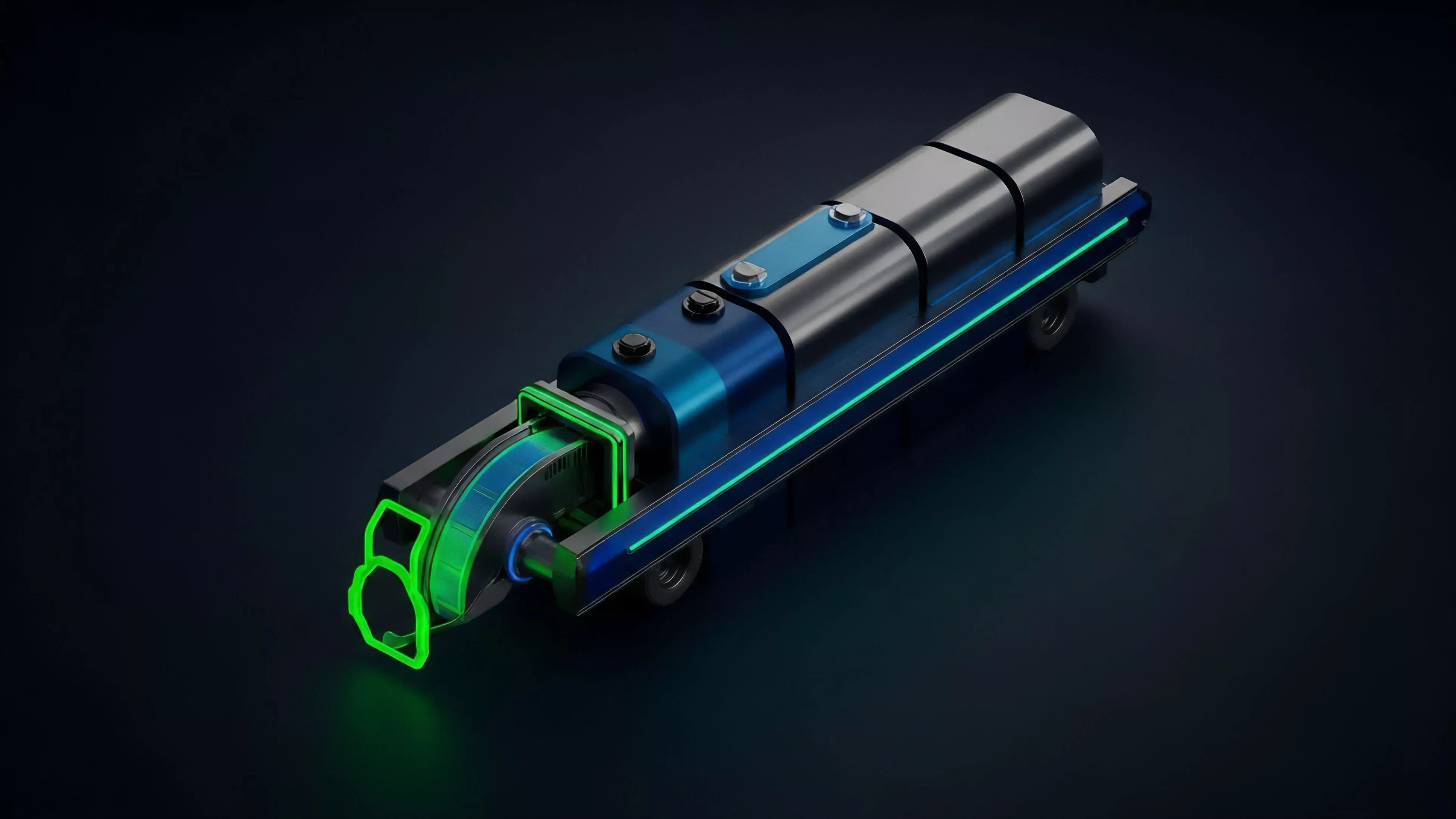

One might observe that the industry currently favors modular hardware integration over monolithic, bespoke systems. This allows for greater interoperability across various blockchain protocols while maintaining a consistent security posture. The reliance on standardized interfaces like PKCS#11 ensures that developers can build derivative engines that are agnostic to the underlying hardware vendor.

Evolution

The path from static hardware tokens to dynamic, cloud-integrated Hardware Security Architecture reflects the shift toward institutional-grade decentralized finance.

Initially, these systems were isolated devices, requiring manual intervention for every transaction. The current state incorporates networked Hardware Security Modules that enable automated, high-throughput signing for institutional derivative desks.

Institutional adoption necessitates hardware-backed security that scales across distributed, high-frequency trading infrastructures.

This evolution mirrors the broader development of decentralized markets. As the demand for sophisticated derivative instruments grows, the underlying hardware must handle increasingly complex logic, such as automated margin calls and multi-asset collateralization, directly within the secure environment. The transition from general-purpose security chips to domain-specific hardware accelerators marks a pivotal shift in the professionalization of the market.

Horizon

The future of Hardware Security Architecture points toward Confidential Computing and the integration of hardware-level support for Zero-Knowledge Proofs.

These advancements will enable complex derivative computations to occur on-chain without exposing the underlying strategy or position data. The objective is to combine the performance of centralized clearing houses with the transparency and trustlessness of decentralized protocols.

| Future Development | Systemic Impact |

|---|---|

| Hardware-accelerated ZK-Proofs | Private, verifiable settlement |

| On-chip protocol validation | Reduced smart contract risk |

| Decentralized Hardware Attestation | Trustless cross-chain interoperability |

We are approaching a state where the hardware itself participates in the consensus process, verifying the validity of derivative trades before they are broadcast to the network. This convergence of protocol physics and physical security will redefine the parameters of risk management, enabling a level of systemic resilience previously unattainable in financial markets.