Essence

Cryptographic Hardware Acceleration defines the utilization of dedicated physical circuitry ⎊ specifically designed silicon ⎊ to execute computationally intensive cryptographic primitives. In the theater of digital finance, this represents the transition from software-defined security to hardware-enforced performance. These systems offload the massive mathematical overhead required for public-key infrastructure, zero-knowledge proof generation, and signature verification from general-purpose CPUs to specialized architectures.

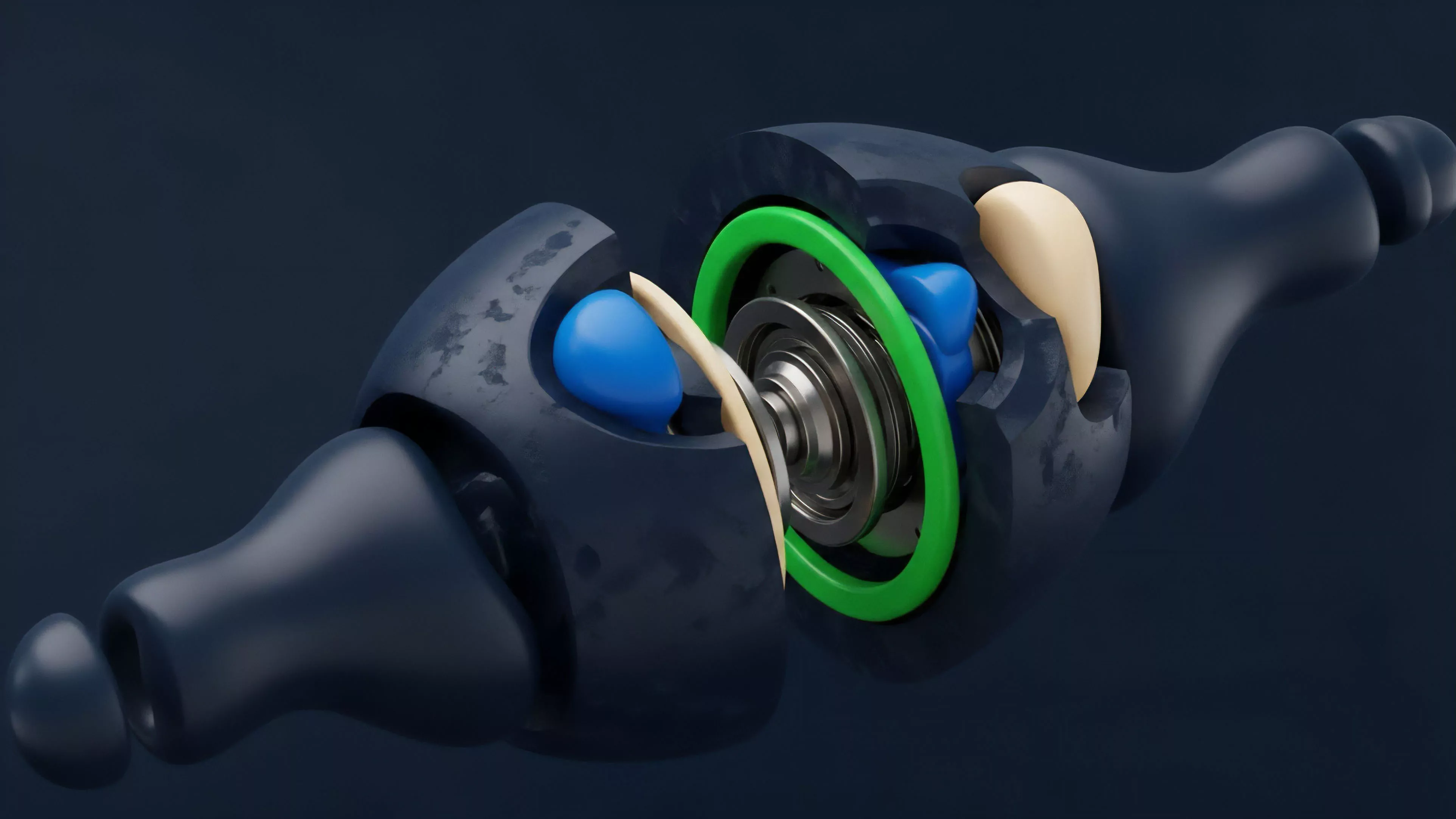

Dedicated cryptographic hardware shifts the computational burden of secure financial verification from software layers to optimized silicon circuits.

The systemic relevance stems from the bottleneck of latency in high-frequency decentralized trading. When throughput demands exceed the capacity of traditional processing units, the security guarantees of a blockchain become a liability rather than an asset. By embedding these operations directly into silicon, the infrastructure gains the ability to process orders and settle trades at speeds that mimic centralized counterparts while maintaining the integrity of decentralized consensus.

Origin

The lineage of Cryptographic Hardware Acceleration traces back to early network security requirements where the need for encrypted communication outpaced the processing power of the era.

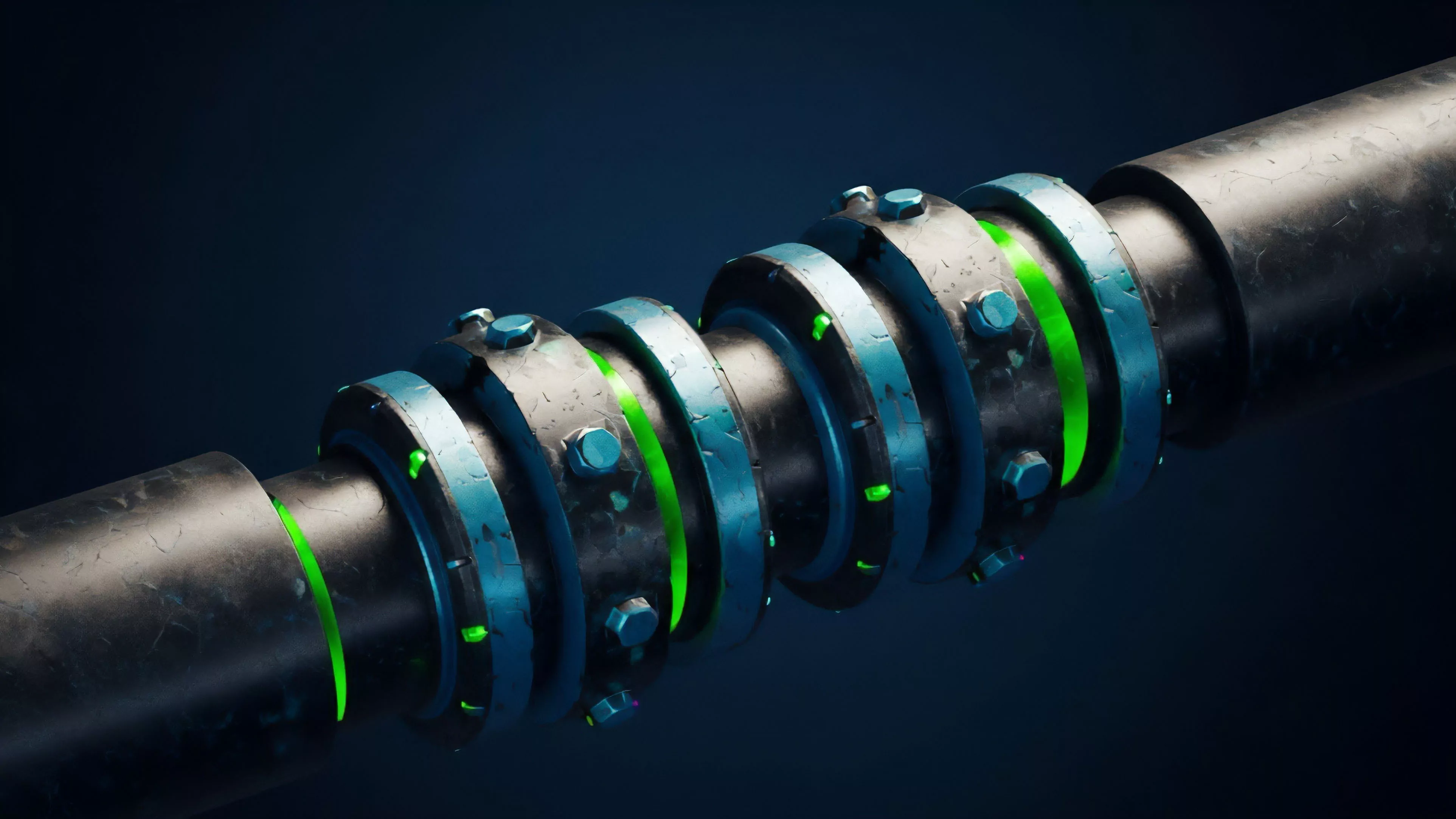

Initial iterations emerged within Hardware Security Modules designed to safeguard private keys in institutional custody environments. These devices provided a physical boundary for sensitive operations, ensuring that cryptographic keys never touched the volatile memory of a general-purpose host machine. As decentralized protocols gained traction, the requirements shifted from simple key protection to massive-scale parallelization of elliptic curve operations.

The evolution moved from centralized HSMs toward field-programmable gate arrays and eventually application-specific integrated circuits tailored for specific hashing algorithms. This transition mirrors the history of financial computing, where the quest for lower latency drives the development of increasingly specialized physical infrastructure.

- Hardware Security Modules provided the foundational concept of isolating cryptographic operations from host software environments.

- Field Programmable Gate Arrays introduced the flexibility to iterate on specialized logic as consensus algorithms evolved.

- Application Specific Integrated Circuits represent the current state of optimization for specific, high-volume cryptographic tasks.

Theory

The mathematical modeling of Cryptographic Hardware Acceleration rests on the efficiency of modular exponentiation and scalar multiplication within finite fields. The primary challenge is the sheer number of operations required for each transaction. By reconfiguring the data path to handle these specific mathematical structures, hardware acceleration reduces the number of clock cycles required per operation by orders of magnitude.

Hardware acceleration optimizes the path of mathematical operations to minimize clock cycles per transaction, enabling scalable financial throughput.

Systems risk enters the frame when considering the centralization of hardware production. If a single entity controls the supply of high-performance silicon, the protocol architecture becomes susceptible to supply-chain manipulation or backdoors. This creates a tension between the need for performance and the requirement for decentralization.

A robust system must account for these hardware-level dependencies, acknowledging that the physical layer of the network is as much a part of the attack surface as the smart contract layer itself.

| Metric | General Purpose CPU | Dedicated Hardware Accelerator |

|---|---|---|

| Throughput | Low | Very High |

| Latency | High | Extremely Low |

| Energy Efficiency | Low | High |

| Development Cost | Low | High |

Approach

Current implementations focus on minimizing the time-to-finality for derivative settlement. By moving the verification of zero-knowledge proofs to hardware, protocols can now execute complex margin calculations and liquidations in real-time. This is where the pricing model becomes truly elegant ⎊ and dangerous if ignored.

The market participant must now factor in the latency advantages of different hardware setups, as those with superior acceleration capabilities effectively gain a speed advantage in front-running or liquidating under-collateralized positions. The strategy involves deploying these accelerators at the edge of the network, closer to the liquidity sources. This proximity reduces the round-trip time for transaction submission and validation.

Anyway, as I was saying, the physics of the protocol dictate the financial outcome; if the hardware layer is optimized for speed, the market will naturally gravitate toward strategies that exploit that speed. This shifts the focus from purely algorithmic trading to a hybrid model where hardware capability is a primary driver of financial performance.

Evolution

The path from early software-based validation to modern silicon-integrated acceleration reflects the broader maturation of decentralized markets. Initially, software was sufficient because transaction volume remained low.

As volumes increased, the latency introduced by software-based verification became a drag on capital efficiency. The shift to hardware was not a choice but a survival requirement for protocols attempting to compete with centralized exchanges.

Hardware integration represents the maturation of decentralized infrastructure, shifting focus from theoretical possibility to competitive financial execution.

We observe a clear progression:

- Software Validation prioritized simplicity and auditability over raw speed.

- Hybrid Acceleration utilized cloud-based FPGA clusters to handle peak demand periods.

- Integrated Silicon embeds verification logic directly into the protocol’s primary processing architecture.

The market now recognizes that hardware performance acts as a silent tax on participants. Those utilizing inferior acceleration face higher slippage and slower execution, effectively subsidizing the operations of faster, hardware-optimized agents. This creates an uneven playing field that is not immediately visible in the smart contract code but is profoundly evident in the order flow and execution data.

Horizon

The future points toward fully autonomous hardware-software co-design.

We anticipate the development of open-source silicon designs that allow any participant to verify the hardware’s integrity, effectively democratizing access to high-performance computing. This will likely lead to a new category of financial derivatives that are specifically designed to be settled on hardware-accelerated rails, creating a new class of assets with deterministic, hardware-guaranteed settlement times.

| Future Phase | Focus | Market Impact |

|---|---|---|

| Open Silicon | Transparency | Increased Trust |

| Autonomous Settlement | Speed | Zero Latency Arbitrage |

| Hardware Governance | Security | Reduced Systemic Risk |

The critical pivot remains the alignment of hardware incentives with protocol decentralization. If the hardware layer becomes a proprietary black box, the entire promise of trustless finance is compromised. The next generation of protocols must treat hardware performance as a first-class citizen in their governance models, ensuring that acceleration serves the network rather than just the fastest participants. What happens when the hardware layer becomes so fast that human-speed decision-making is rendered entirely obsolete?