Low-Latency Proofs

Meaning ⎊ Low-Latency Proofs enable instantaneous cryptographic verification of complex financial states, facilitating high-frequency decentralized trading.

ZK-Proof Finality Latency

Meaning ⎊ ZK-Proof Finality Latency measures the temporal lag between transaction execution and cryptographic settlement, defining the bounds of capital efficiency.

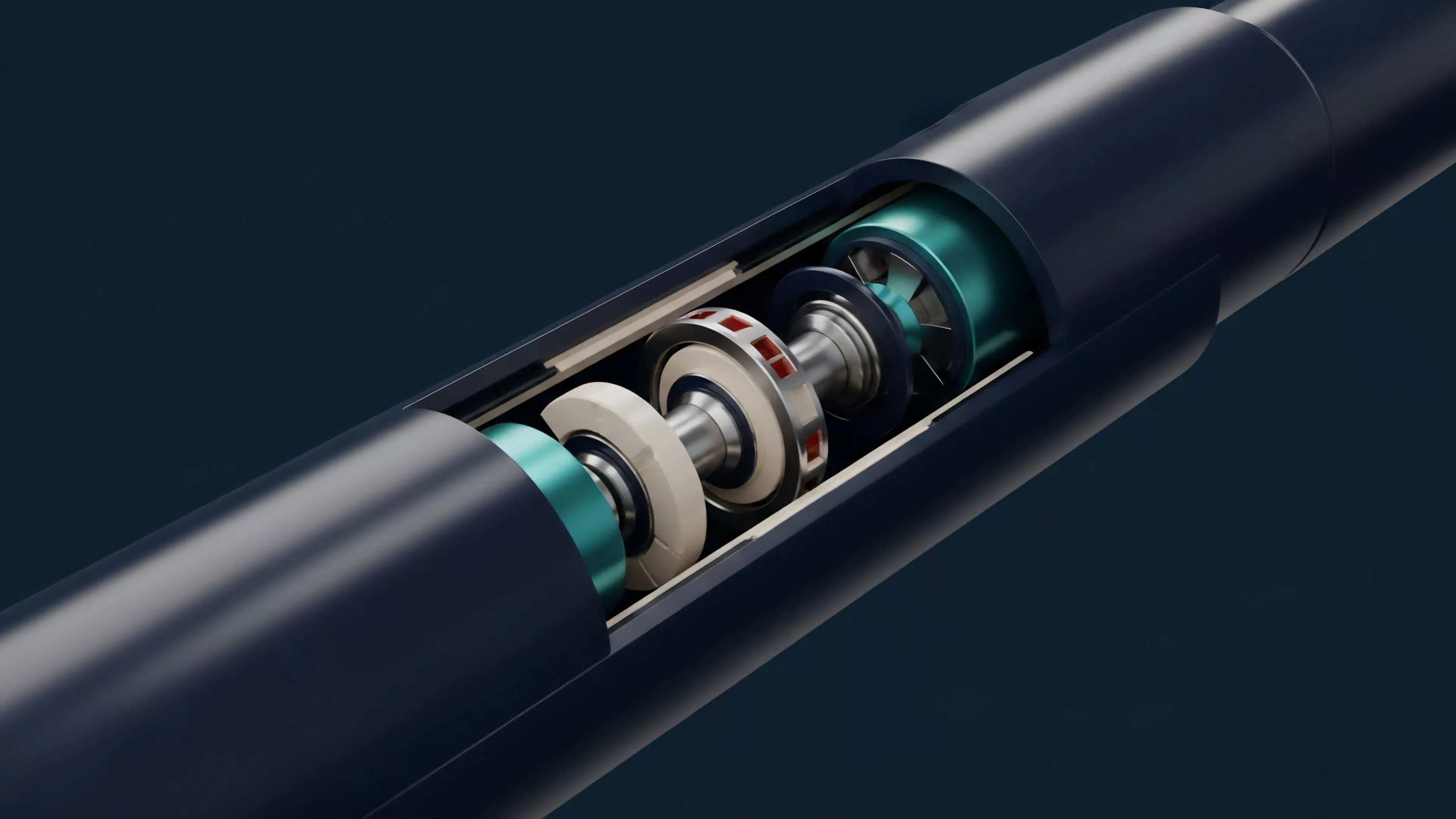

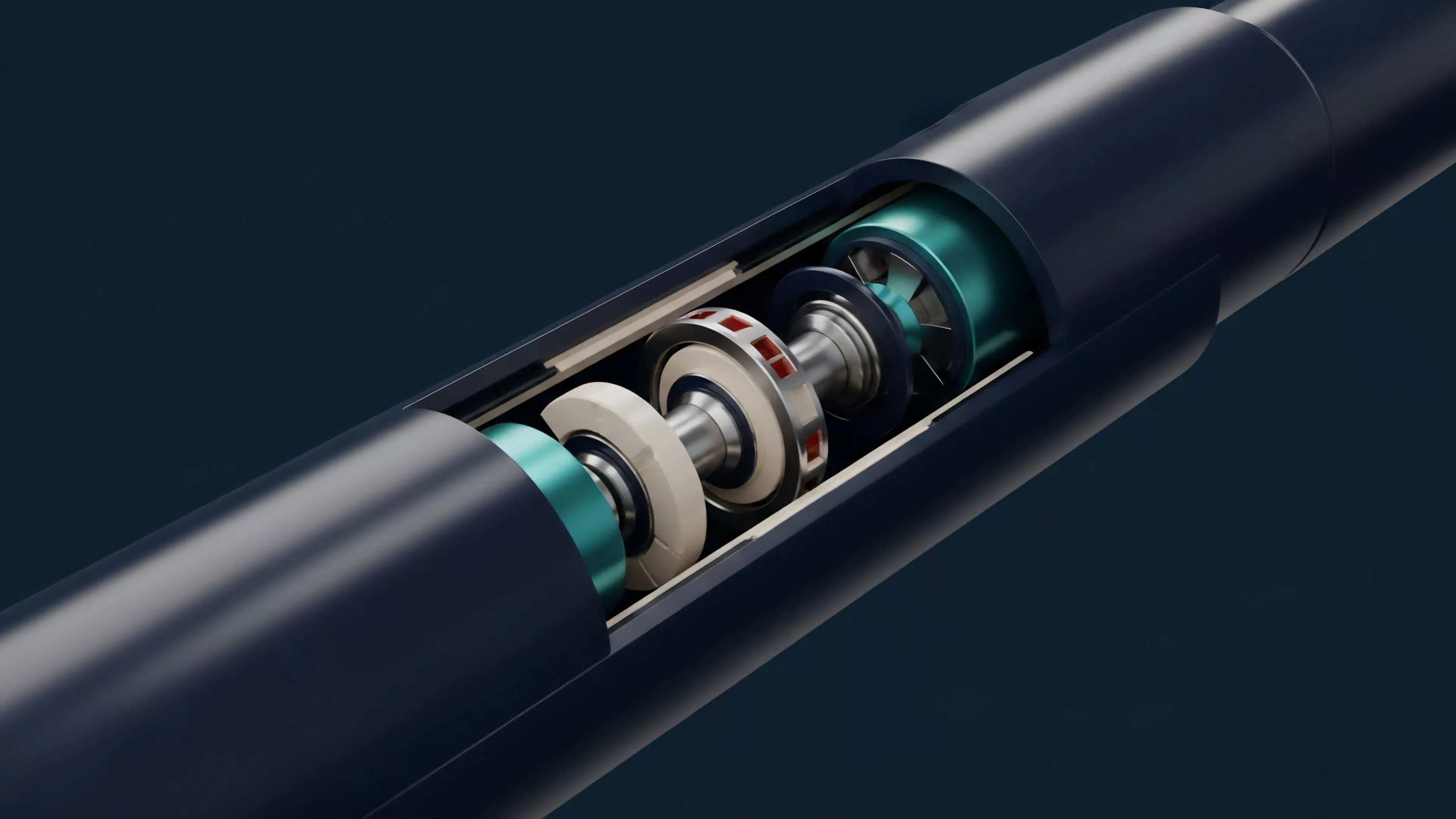

Proof Generation Latency

Meaning ⎊ Proof Generation Latency is the quantifiable time delay for cryptographic verification that dictates the risk window and capital efficiency of decentralized derivatives settlement.

Latency-Risk Trade-off

Meaning ⎊ The Latency-Risk Trade-off, or The Systemic Skew of Time, defines the non-linear exchange of execution speed for exposure to protocol-level and settlement uncertainty in crypto derivatives.

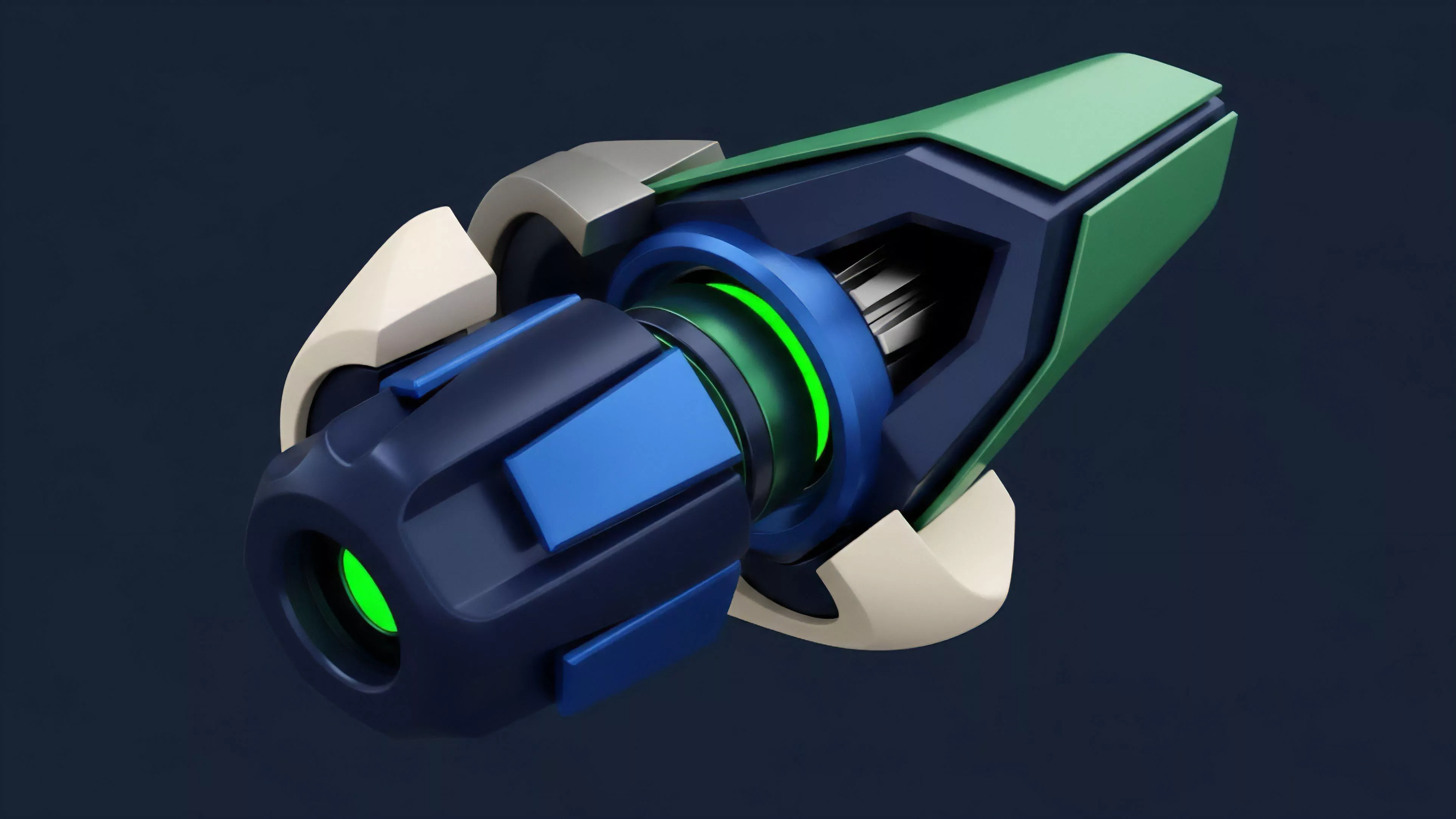

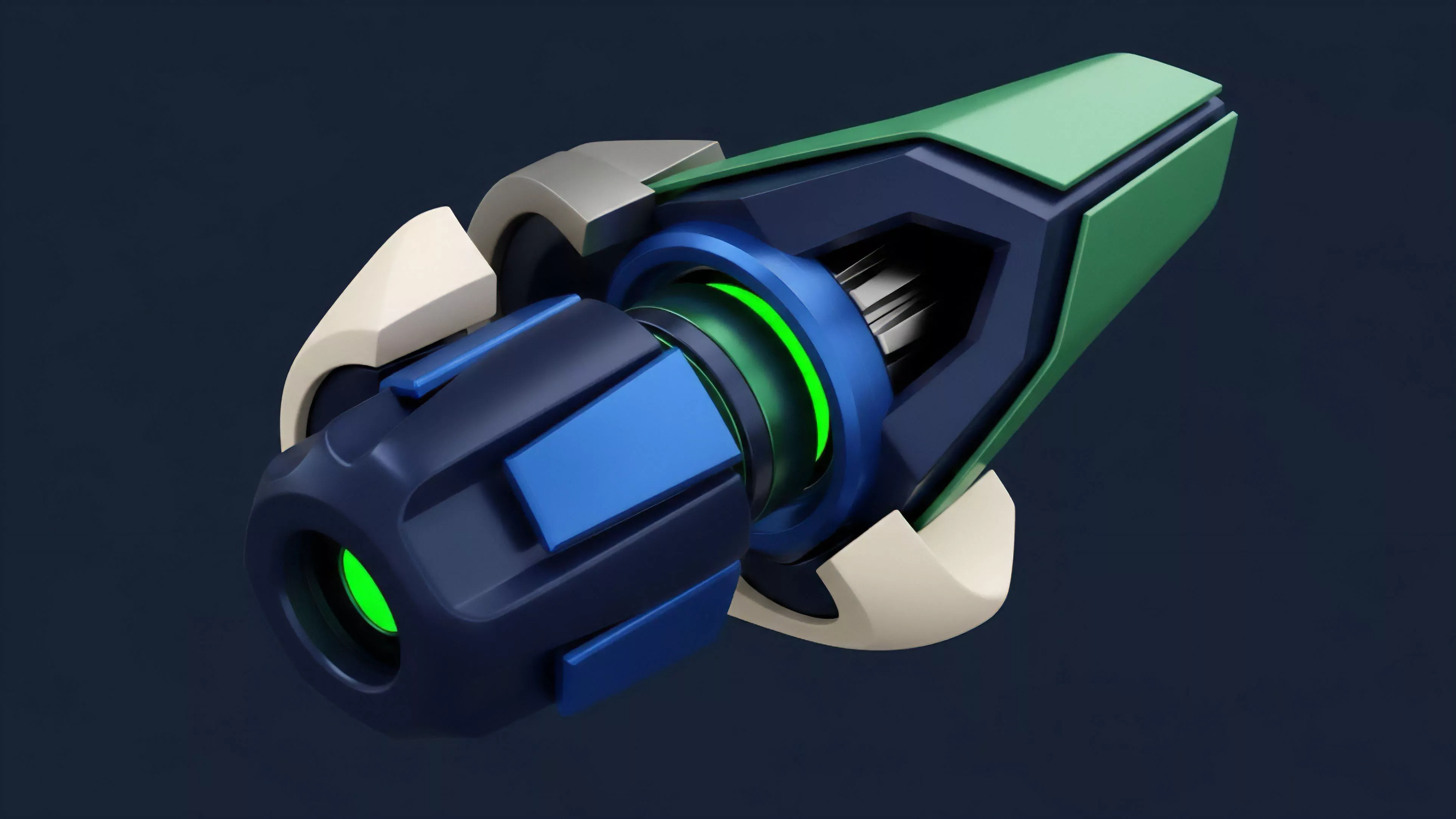

Settlement Latency

Meaning ⎊ The duration between trade execution and the final, irreversible legal and technical transfer of asset ownership.