Real-Time Proving

Meaning ⎊ Real-Time Proving establishes immediate cryptographic certainty of protocol solvency, eliminating counterparty risk through continuous validation.

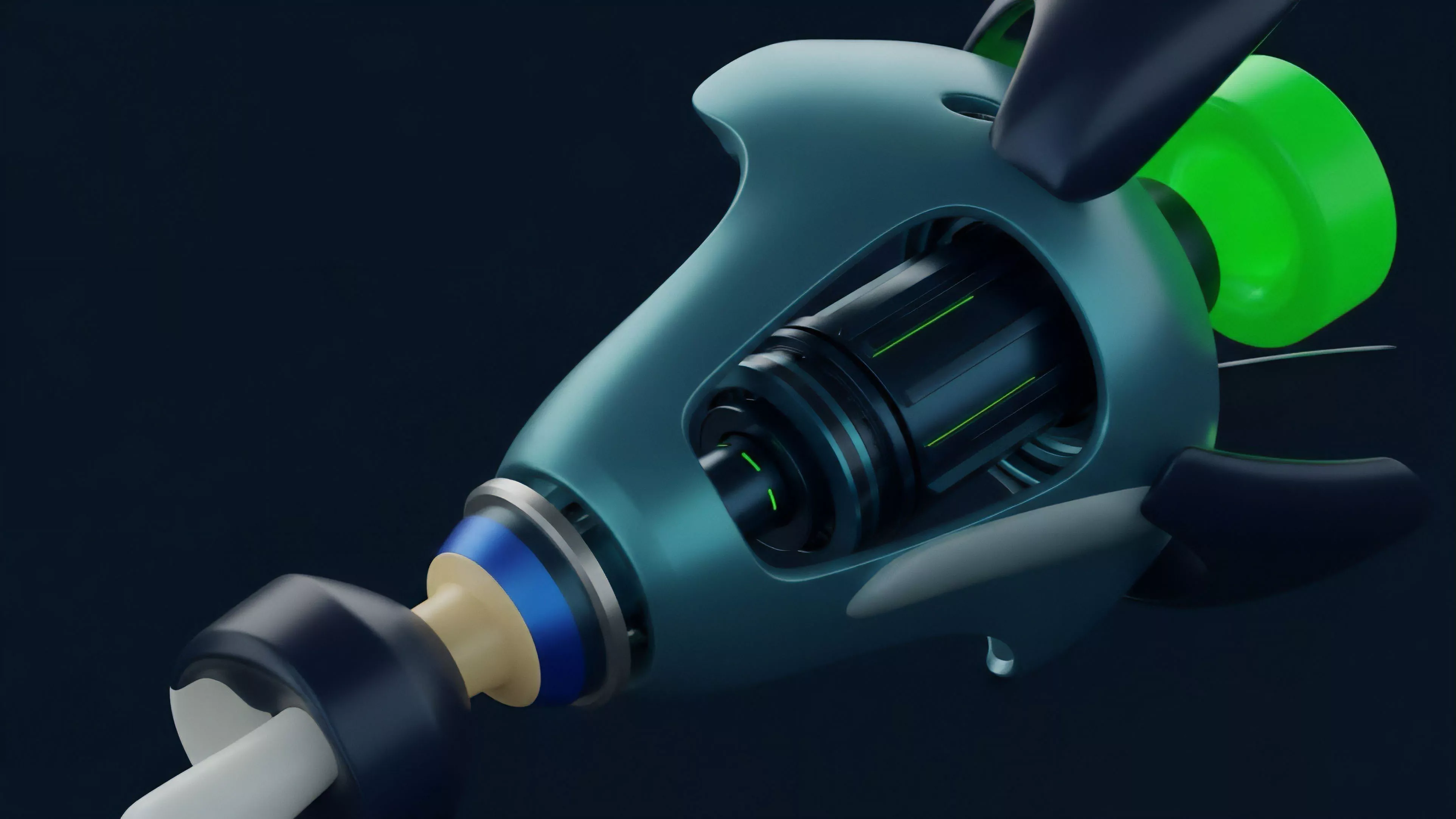

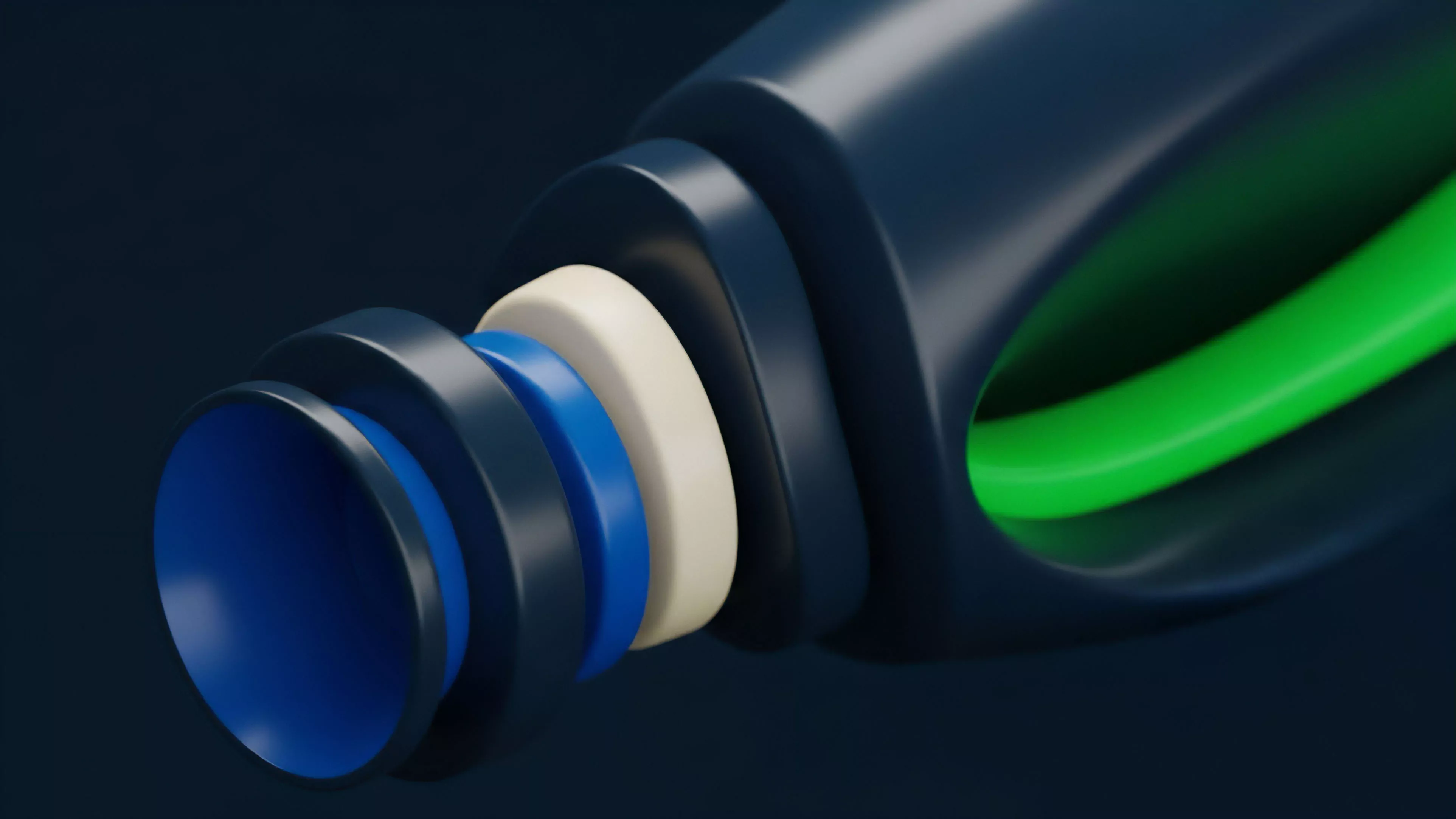

Hardware Security Modules

Meaning ⎊ Physical, tamper-resistant devices designed to store and manage cryptographic keys securely within isolated environments.

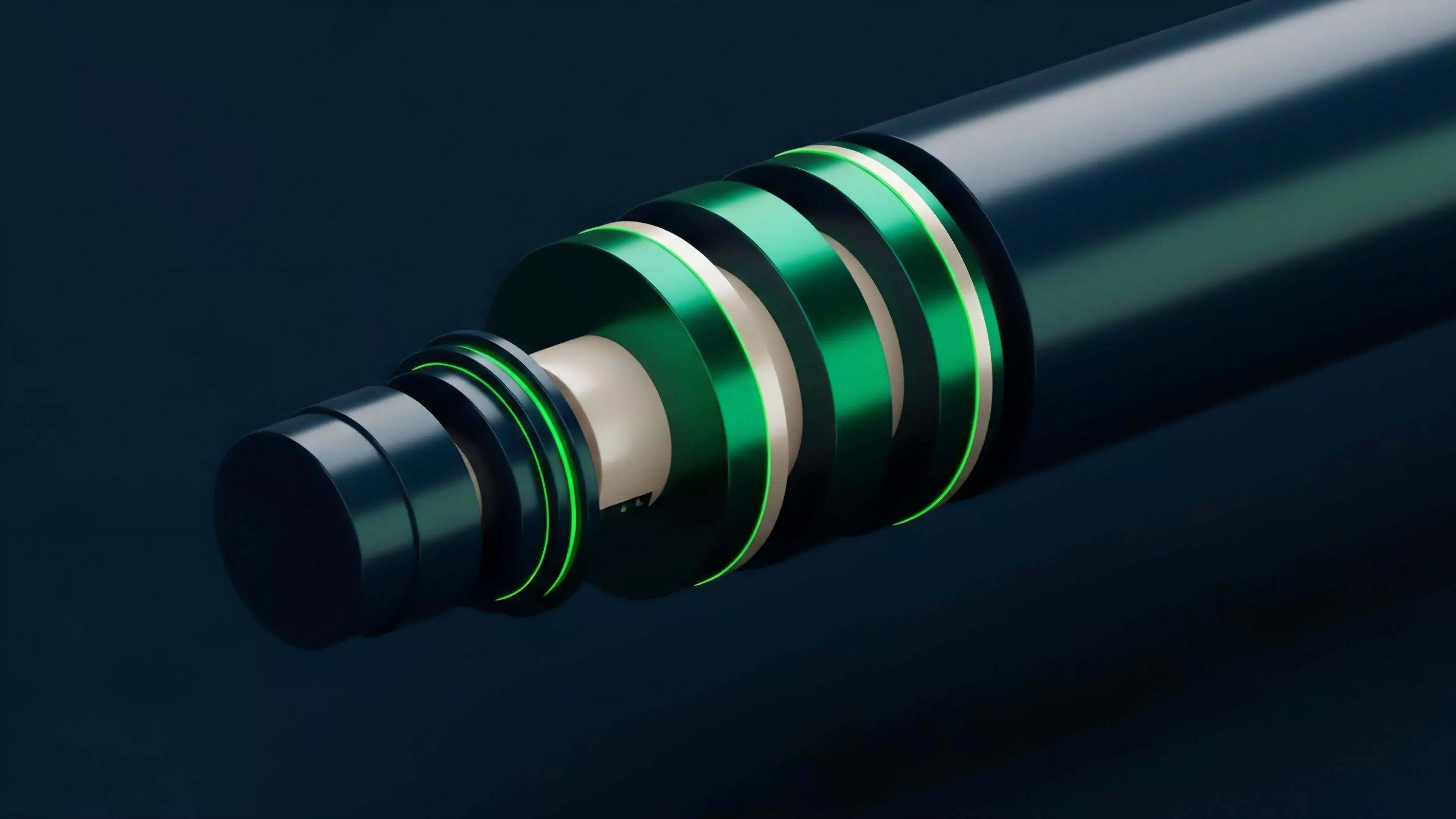

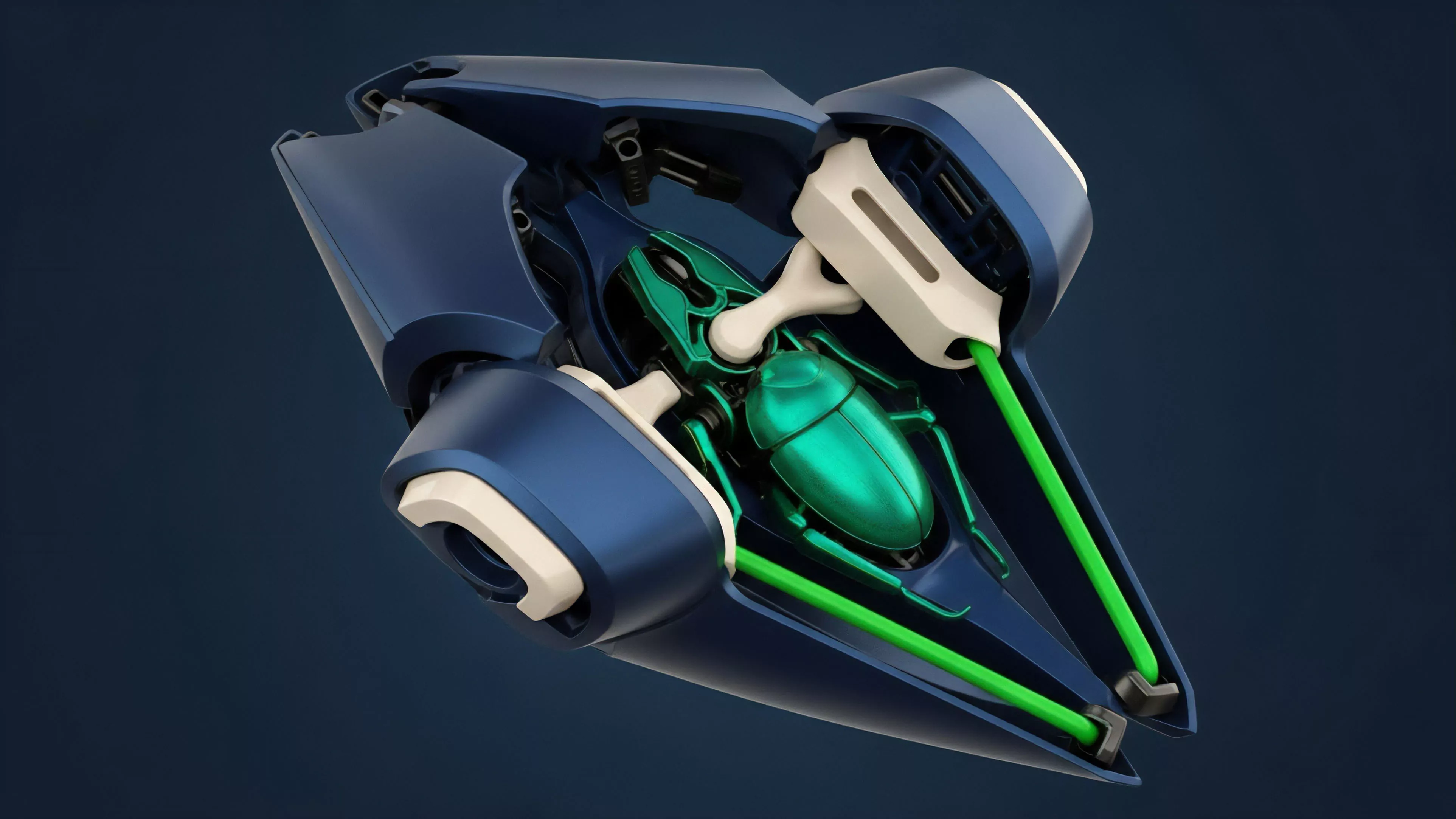

Hardware Acceleration

Meaning ⎊ Utilizing specialized hardware to perform high-speed computations and reduce latency in financial transactions.

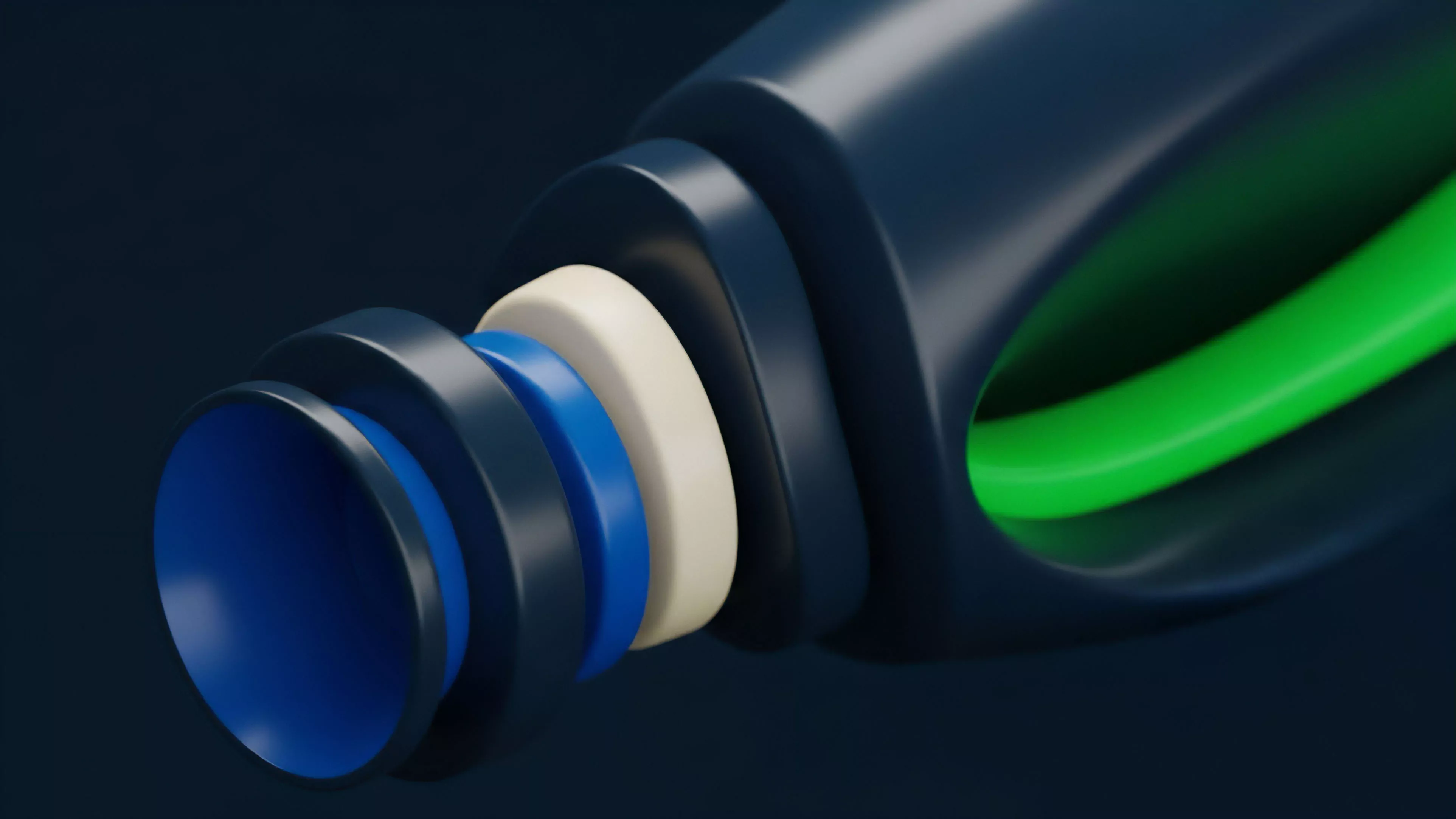

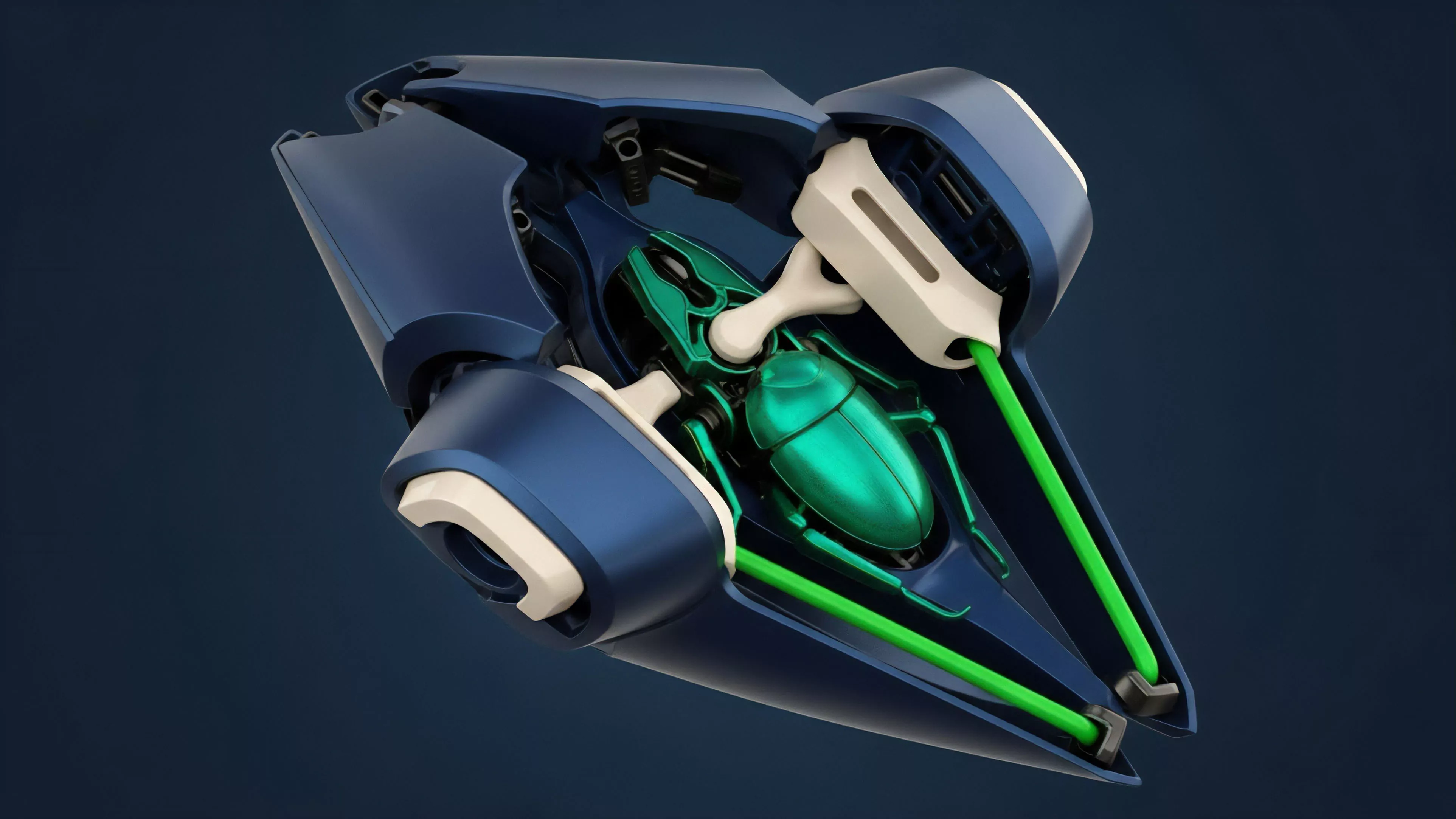

Off Chain Proof Generation

Meaning ⎊ Off Chain Proof Generation decouples complex financial computation from public ledgers, enabling private, scalable, and mathematically verifiable trade settlement.